Студентам > Курсовые > Развитие технологии МОП ИС

Развитие технологии МОП ИССтраница: 2/7

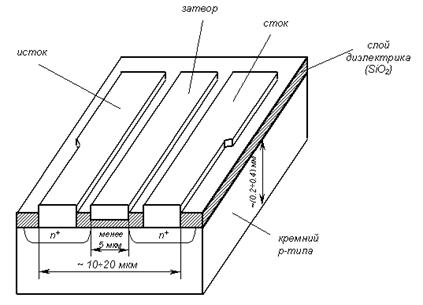

Рисунок – 2.1 - Структура n-канального МОП – транзистора

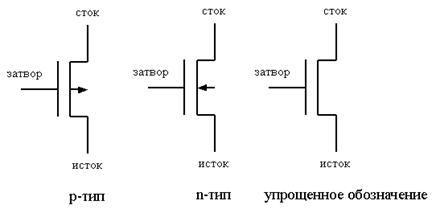

На рис. 2.2 показаны стандартные обозначения n МОП- и p МОП - транзисторов.

Рисунок 2.2 - Обозначения n МОП- и p МОП – транзисторов

3 Технология n – канальных МОП СБИС

Полевой транзистор на основе структуры металл – окисел – полупроводник (МОП ПТ) наиболее широко используется в СБИС. До начала 70 – х гг. доминировали интегральные схемы на основе p – канальных МОП ПТ, что было связано с низким качеством окисла и границы раздела SiO2/Si. В результате возникали заряды, приводящие к инверсии типа проводимости на поверхности подложки p – типа. После 70 – х гг. доминируют n – канальные МОП ИС, преимущество которых проявляется в более высокой подвижности электронов по сравнению с дырками, и, следовательно, в большем быстродействии ИС.

С технологической точки зрения изготовление МОП – транзисторов значительно проще биполярных транзисторов. Это можно видеть из сравнительного анализа данных таблицы 3.1.

Таблица 3.1 – Сравнение ключевых процессов и условий технологии производства биполярных и МОП – интегральных схем. |

Биполярная технология |

МОП - технология | |

4-7 процессов легирования (имплантация и/или диффузия)

Необходимость полной изоляции элементов (изолированных островков)

Эпитаксиальный процесс является одной из основных операций

Используется от 6 до 8 фотолитографий

Более 100 технологических операций

10 процессов с температурой около (или выше) 1000 C

Коэффициент передачи транзистора зависит от режимов легирования и термообработки |

1-3 процесса легирования (имплантация, диффузия)

К изоляции предъявляются менее жёсткие требования

Эпитаксиальный процесс не обязателен

Используется 4 - 6 фотолитографий

Около 30 технологических операций

2 процесса с температурой около (или выше) 1000 C

Коэффициент передачи транзистора существенно не зависит от режимов легирования |

МОП - транзистор имеет малую площадь и, обладая высоким входным сопротивлением, потребляет малую мощность от источника сигнала. В дополнение, при нулевом напряжении на затворе МОП ПТ с индуцированным каналом ток стока практически отсутствует, т. е. мощность потребляется транзистором только во время подачи напряжения на затвор. Процесс изготовления МОП - интегральных схем сводится к формированию МОП – транзисторов и соединений между ними, поскольку МОП - структуры могут использоваться не только в качестве транзисторов, но и как резисторы и конденсаторы, т. е. практически все схемные функции можно реализовать на одних МОП - структурах.

Рисунок 3.1 - Схема изготовления МОП ИМ с самосовмещенными поликремниевыми затворами; а — выращивание маскирующего оксида и первая фотолитография; б — выращивание подзатворного оксида; в — наращивание поликристаллического кремния; г — вторая фотолитография; д — диффузия областей истоков и стоков; е — осаждение плевки оксида; ж — третья фотолитография, формирование металлизации

Благодаря вышеуказанным факторам, МОП - интегральные схемы заняли ведущее положение в области цифровой обработки информации. Рассмотрим типичный технологический процесс изготовления МОП – транзистора с LOCOS-изоляцией. На рисунке 3.1 представлены основные этапы технологического процесса, а в разделах 3.1 – 3.7 более подробное их описание.

3.1 Исходный материал

Исходный материал - подложки слаболегированного (порядка  ) кремния р - типа с ориентацией поверхности вдоль (001) плоскости. Выбор подложек с ориентацией (001) обусловлен значительно меньшей (на порядок) плотностью поверхностных состояний по сравнению с ориентацией (111). При выборе уровня легирования подложки принимают во внимание следующие обстоятельства. Чем слабее легирована подложка, тем менее чувствительно пороговое напряжение транзистора к смещению на подложке и тем меньшая емкость возникает между областями истока, стока и подложкой. Однако если подложка легирована слишком слабо, обедненные области истока и стока могут соприкасаться, приводя к проколам транзисторов. В дополнение, слаболегированные подложки имеют высокую концентрацию неосновных носителей заряда, что увеличивает токи утечки p-n-переходов при их обратном смещении. Эту проблему можно решить двумя способами. Один из них заключается в выращивании слаболегированных (~ ) кремния р - типа с ориентацией поверхности вдоль (001) плоскости. Выбор подложек с ориентацией (001) обусловлен значительно меньшей (на порядок) плотностью поверхностных состояний по сравнению с ориентацией (111). При выборе уровня легирования подложки принимают во внимание следующие обстоятельства. Чем слабее легирована подложка, тем менее чувствительно пороговое напряжение транзистора к смещению на подложке и тем меньшая емкость возникает между областями истока, стока и подложкой. Однако если подложка легирована слишком слабо, обедненные области истока и стока могут соприкасаться, приводя к проколам транзисторов. В дополнение, слаболегированные подложки имеют высокую концентрацию неосновных носителей заряда, что увеличивает токи утечки p-n-переходов при их обратном смещении. Эту проблему можно решить двумя способами. Один из них заключается в выращивании слаболегированных (~ ) эпитаксиальных слоев р – типа на сильнолегированных подложках р - типа (~ ) эпитаксиальных слоев р – типа на сильнолегированных подложках р - типа (~ ). Сильнолегированные подложки имеют низкую концентрацию неосновных носителей заряда (электронов), поэтому диффузионный ток в обратно смещенных переходах подавляется несмотря на большую диффузионную длину неосновных носителей в эпитаксиальном слое. Второй подход к решению проблемы основан на использовании эффекта внутреннего гетерирования. На глубине подложки формируют преципитаты Si02, которые существенно снижают время жизни неосновных носителей заряда при одновременной очистке приповерхностных областей подложки. ). Сильнолегированные подложки имеют низкую концентрацию неосновных носителей заряда (электронов), поэтому диффузионный ток в обратно смещенных переходах подавляется несмотря на большую диффузионную длину неосновных носителей в эпитаксиальном слое. Второй подход к решению проблемы основан на использовании эффекта внутреннего гетерирования. На глубине подложки формируют преципитаты Si02, которые существенно снижают время жизни неосновных носителей заряда при одновременной очистке приповерхностных областей подложки.

3.2 Изоляция

При переходе к высокой степени интеграции СБИС особую роль приобретает изоляция отдельных активных транзисторов для подавления паразитных электрических связей. На рисунке 3.2 показаны два смежных n - канальных МОП ПТ. Направление проводимости активных транзисторов перпендикулярно поликремневому затвору. Однако под затвором между соседними транзисторами могут возникать паразитные транзисторы, как это показано на рисунке 3.1.

Рисунок 3.2 – Топология смежных n – канальных МОП ИТ с общим поликремневым затвором, демонстрирующая появление паразитных транзисторов: а – вид сверху, на котором отмечены как активный, так и паразитные транзисторы; б – поперечное сечение по A-A соответствует структуре с LCMOS – изоляцией. Области p+, проникающие в подложку, ограничивают распространение канала и препятствуют формированию паразитных транзисторов.

Для того чтобы устранить возможность появления проводимости между соседними транзисторами, пороговое напряжение паразитных транзисторов должно быть очень высоким. Это достигается путем формирования толстого заглубленного слоя окисла между активными транзисторами. При формировании МОП ПТ используют LOCMOS – изоляцию, основанную на локальном окислении предварительно протравленных участков кремния.

|

Главная

Главная

Схемы

Схемы

Студентам

Студентам

Программы

Программы

Поиск

Поиск

Top50

Top50

Главная

Главная

Схемы

Схемы

Студентам

Студентам

Программы

Программы

Поиск

Поиск

Top50

Top50