Студентам > Рефераты > ПЛИС Xilinx семейства Virtex

ПЛИС Xilinx семейства VirtexСтраница: 3/15

Архитектура Virtex также включает следующие элементы, которые соединяются с матрицей ГТМ:

• Специальные блоки памяти (BRAMs) размером 4096 бит каждый.

• Четыре модуля автоподстройки задержек (DLL), предназначенных для компенсации задержек тактовых сигналов, а также деления, умножения и сдвига фазы тактовых частот.

• Буферы с тремя состояниями (BUFT), которые расположены вблизи каждого КЛБ и управляют горизонтальными сегментированными трассами.

Коды, записанные в ячейки статической памяти, управляют настройкой логических элементов и коммутаторами трасс, осуществляющих соединения в схеме. Эти коды загружаются в ячейки после включения питания и могут перезагружаться в процессе работы, если необходимо изменить реализуемые микросхемой функции.

4.2. Блок ввода-вывода

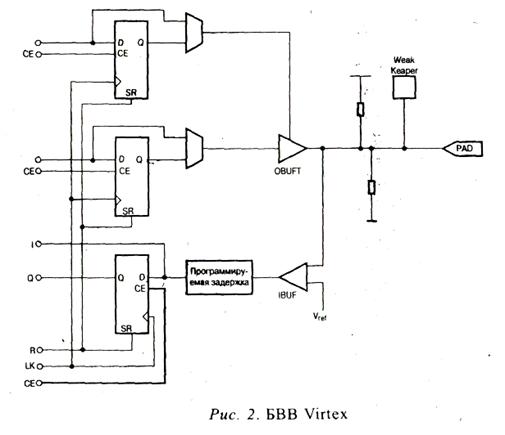

Основным отличительным свойством EBB семейства Virtex является поддержка широкого спектра стандартов сигналов ввода-вывода. На Рис. 2 представлена структурная схема БВВ. В Табл. 3 перечислены поддерживаемые стандарты.

Таблица 3. Поддерживаемые стандарты ввода-вывода. | Стандарт ввод/вывод | Напряжение порогового уровня входных каскадов,  | Напряжение питания выходных каскадов,  | Напряжение согласования с платой,  | 5-В совместимость | | LVTTL | нет | 3.3 | нет | да | | LVCMOS2 | нет | 2.5 | нет | да | | PCI, 5 A | нет | 3.3 | нет | да | | PCI, 3.3 A | нет | 3.3 | нет | нет | | GTL | 0.8 | нет | 1.2 | нет | | GTL+ | 1.0 | нет | 1.5 | нет | | HSTL Class I | 0.75 | 1.5 | 0.75 | нет | | HSTL Class III | 0.9 | 1.5 | 1.5 | нет | | HSTL Class IV | 0.9 | 1.5 | 1.5 | нет | | SSTL3 Class I & II | 1.5 | 3.3 | 1.5 | нет | | SSTL2 Class I & II | 1.25 | 2.5 | 1.25 | нет | | CTT | 1.5 | 3.3 | 1.5 | нет | | AGP | 1.32 | 3.3 | нет | нет |

БВВ содержит три запоминающих элемента, функционирующих либо как D-тригтеры, либо как триггеры-защелки. Каждый БВВ имеет входной сигнал синхронизации (CLK), распределенный на три триггера и независимые для каждого триггера сигналы разрешения тактирования (Clock Enable — СЕ).

Кроме того, на все триггеры заведен сигнал сброса/установки (Set/Reset-SR). Для каждого триггера этот сигнал может быть сконфигурирован независимо, как синхронная установка (Set), синхронный сброс (Reset), асинхронная предустановка (Preset) или асинхронный сброс (Clear).

Входные и выходные буферы, а также все управляющие сигналы в БВВ допускают независимый выбор полярности. Данное свойство не отображено на блок-схеме БВВ, но контролируется программой проектирования.

Все контакты защищены от повреждения электростатическим разрядом и от всплесков перенапряжения. Реализованы две формы защиты от перенапряжения, олдна допускает 5-В совместимость, а другая нет. Для случая 5-В совместимости, структура, подобная диоду Зенера, закорачивает на землю контакт, когда напряжение на нем возрастает приблизительно до 6.5В. В случае, когда требуется 3.3-В PCI-совместимость, обычные диоды ограничения могут подсоединяться к источнику питания выходных каскадов,   . Тип защиты от перенапряжения может выбираться независимо для каждого контакта. По выбору, к каждому контакту может подключаться: . Тип защиты от перенапряжения может выбираться независимо для каждого контакта. По выбору, к каждому контакту может подключаться:

1. Резистор, соединенный с общей шиной питания (pull-down).

2. Резистор, соединенный с шиной питания (pull-up).

3. Маломощная схема удержания последнего состояния (week-keeper).

До начала процесса конфигурирования микросхемы все выводы, не задействованные в этом процессе, принудительно переводятся в состояние высокого импеданса. Резисторы «pull-down» и элементы «week-keeper» неактивны, а резисторы «pull-up» можно активировать.

Активация резисторов «pull-up» перед конфигурацией управляется внутренними глобальными линиями через управляющие режимные контакты. Если резисторы «pull-up» не активны, то выводы находятся в состоянии неопределенного потенциала. Если в проекте необходимо иметь определенные логические уровни до начала процесса конфигурирования нужно использовать внешние резисторы.

|

Главная

Главная

Схемы

Схемы

Студентам

Студентам

Программы

Программы

Поиск

Поиск

Top50

Top50

Главная

Главная

Схемы

Схемы

Студентам

Студентам

Программы

Программы

Поиск

Поиск

Top50

Top50