Студентам > Курсовые > Разработка схемы электронного эквалайзера

Разработка схемы электронного эквалайзераСтраница: 9/10

Рис.12.

Схема интерфейса между двумя устройствами (АЦП и DSP) показана на рис. 13. В качестве сигнала окончания преобразования от AD7854/AD7854L используется сигнал BUSY. Нужно заметить, что показанная конфигурация позволяет DSP-процессору записывать данные в регистр управления параллельным интерфейсом AD7854/AD7854L. Это необходимо для установки различных опций в AD7854/AD7854L и выполнения процесса калибровки. Однако в обычном режиме чтение данных из AD7854/AD7854L осуществляется в соответствии с приведенным выше описанием. Запись в периферийные устройства, включенные в адресное пространство памяти, рассматривается в последующих разделах этой главы.

Параллельные интерфейсы между другими DSP-процессорами и внешними периферийными устройствами могут быть построены подобным способом, однако всякий раз необходимо тщательно изучить временные параметры всех соответствующих сигналов для каждого устройства. Техническая документация большинства АЦП содержит достаточную информацию для организации интерфейса с DSP-процессорами.

Рис.13. Описание ЦАП

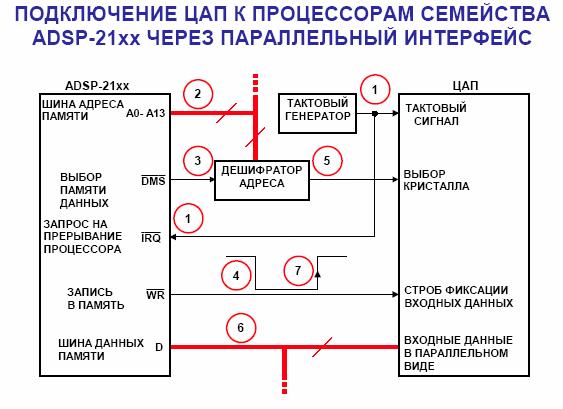

ОРГАНИЗАЦИЯ ПАРАЛЛЕЛЬНОГО ИНТЕРФЕЙСА С DSP-ПРОЦЕССОРАМИ: ЗАПИСЬ ДАННЫХ В ЦАП, ПОДКЛЮЧЕННЫЙ С ОТОБРАЖЕНИЕМ В АДРЕСНОЕ ПРОСТРАНСТВО ПАМЯТИ.

Схема стандартного интерфейса между DSP-процессором и параллельным периферийным устройством (например ЦАП) показана на рис. 14.

В большинстве приложений реального времени ЦАП функционирует непрерывно с постоянной тактовой частотой. Большинство ЦАП, используемых для этих приложений, осуществляет двойную буферизацию данных. Имеется входной регистр для фиксации данных, поступающих через асинхронный интерфейс с DSP-процессором, и далее регистр (называемый регистром хранения ЦАП), который управляет токовыми ключами ЦАП. Регистр хранения ЦАП синхронизируется внешним стабильным генератором, задающим частоту дискретизации. Кроме тактирования регистра хранения ЦАП, данный сигнал используется также для генерации сигнала прерывания DSP-процессора, который указывает на готовность ЦАП к приему новых входных данных.

Рис.14.

Таким образом, процесс записи инициируется периферийным устройством посредством установления сигнала запроса прерывания DSP-процессора, указывающего, что периферийное устройство готово к приему новых данных (шаг N 1). Далее DSP-процессор выставляет адрес периферийного устройства на адресной шине (шаг N 2) и переводит в активное состояние сигнал выбора памяти DMS (шаг N 3). Это приводит к тому, что дешифратор адреса выдает сигнал выбора (chip select) на периферийное устройство (шаг N 5). После спадающего (переднего) фронта сигнала DMS через промежуток времени tASW процессор переводит в активное нулевое состояние сигнал записи WR (шаг N 4). Длительность импульса WR составляет tWP нс. Данные помещаются на шину данных (D) и удерживаются в течение времени tDW, до перехода сигнала WR в неактивное единичное состояние (шаг N 6). Восходящий (задний) фронт сигнала WR используется для фиксации присутствующих на шине данных (D) во внешнюю параллельную память (шаг N 7). Данные на шине остаются достоверными еще в течение времени tDH после прохождения положительного фронта сигнала WR.

Основные требования по временным параметрам при записи данных в периферийное устройство показаны на рис. 14. Главным параметром здесь является длительность строба записи tWP. Для всех периферийных устройств, кроме самых быстрых, придется использовать циклы ожидания, т.к. этим устройствам нужно больше времени для доступа к данным.

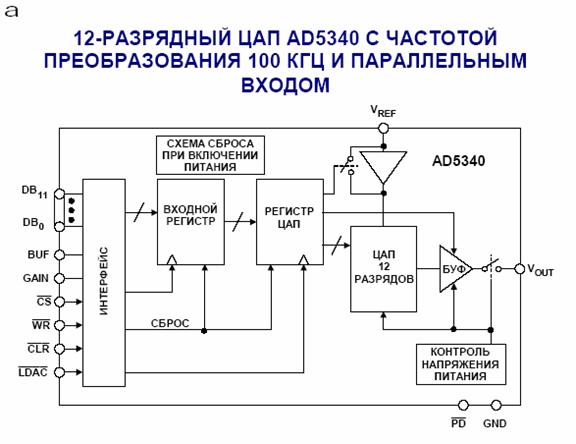

Микросхема AD5340 – это 12-ти разрядный ЦАП, работающий на частоте дискретизации 100 кГц, имеющий параллельный цифровой интерфейс. Данный АЦП питается от однополярного источника питания напряжением +2.5-5.5 В и рассеивает мощность 345 мкВт (при напряжении питания 3 В). В энергосберегающем режиме потребляемая мощность прибора снижается до 0.24 мкВт. ЦАП AD5340 имеет в своем составе выходной буферный усилитель, который способен формировать выходной сигнал в диапазоне значений от нуля до напряжения питания. В ИС AD5340 можно задействовать или отключить встроенный буфер для источника опорного напряжения. В устройстве имеется встроенная схема формирования сигнала сброса при включении питания, гарантирующая нулевое значение сигнала на выходе ЦАП до тех пор, пока в ЦАП не будут записаны корректные данные. Структурная схема ЦАП показана на рис. 15. На входе прибора осуществляется двойная буферизация данных. Спецификация временных параметров цикла записи для ADSP-2189M дается для тактовой частоты 75 МГц.

Рис.15.

Исследование временных характеристик, изображенных на рис. 7.14, показывает, что для обеспечения совместимости по синхронизации между устройствами потребуется программирование двух циклов ожидания в процессоре ADSP-2189M. Это позволяет увеличить длительность строба записи (WR) до 30.25 нс, что превышает минимально необходимую длительность строба записи в ЦАП AD5340 (20 нс). Минимальное время установления данных в микросхеме AD5340, равное 5 нс, также перекрывается при использовании двух циклов ожидания. Схема интерфейса между двумя устройствами показана на рис. 16.

Параллельные интерфейсы с другими DSP-процессорами могут быть организованы подобным образом, для чего необходимо подробное изучение временных спецификаций всех соответствующих сигналов каждого из взаимодействующих устройств.

Рис.16.

Рис. 17. Принципиальная схема DSP системы.

Алгоритм работы устройства ADSP-21XX

|

распределение памяти для коэффициентов аi | |

|

Главная

Главная

Схемы

Схемы

Студентам

Студентам

Программы

Программы

Поиск

Поиск

Top50

Top50

Главная

Главная

Схемы

Схемы

Студентам

Студентам

Программы

Программы

Поиск

Поиск

Top50

Top50