Студентам > Курсовые > Разработка схемы электронного эквалайзера

Разработка схемы электронного эквалайзераСтраница: 8/10

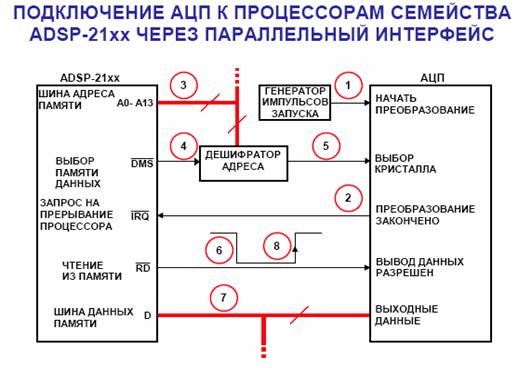

Рис.10. Описание АЦП

В связи с быстрым развитием технологии смешанной аналогово-цифровой обработки сигналов устройства на базе DSP с высокой степенью интеграции, появляющиеся на рынке в настоящее время (например ADSP-21ESP202), имеют помимо DSP-ядра интегрированные АЦП/ЦАП, что снимает проблему организации интерфейса между отдельными компонентами. Дискретные АЦП и ЦАП теперь оснащаются интерфейсами, специально предназначенными для связи с DSP, и тем самым минимизируют или устраняют необходимость внешней поддержки интерфейса или применения интерфейсной логики. Высокопроизводительные сигма-дельта-АЦП и ЦАП в настоящее время выпускаются в одном корпусе (такое комбинированные решение называется КОДЕК или КОдер/ДЕКодер), например, AD73311 и AD73322. Данные устройства также разработаны с учетом минимальных требований к интерфейсной логике при работе с наиболее распространенными DSP-процессорами. В настоящей главе рассматриваются проблемы, связанные с передачей и синхронизацией данных при организации различных интерфейсов.

ОРГАНИЗАЦИЯ ПАРАЛЛЕЛЬНОГО ИНТЕРФЕЙСА С DSP-ПРОЦЕССОРАМИ: ЧТЕНИЕ ДАННЫХ ИЗ АЦП, ПОДКЛЮЧЕННОГО С ОТОБРАЖЕНИЕМ В АДРЕСНОЕ ПРОСТРАНСТВО ПАМЯТИ

Подключение АЦП или ЦАП через быстрый параллельный интерфейс к DSP-процессору требует понимания специфики процессов чтения данных DSP-процессором из периферийных устройств (АЦП), а также записи данных процессором в периферийные устройства (ЦАП) при подключении данных устройств в адресное пространство памяти. Вначале мы рассмотрим некоторые основные требования к временным параметрам сигналов, используемых для чтения и записи данных. Необходимо отметить, что принципы, представленные здесь на примере доступа к АЦП и ЦАП, применимы также при чтении и записи в/из внешней памяти.

Блок-схема типичного параллельного интерфейса DSP-процессора с внешним АЦП показана на рис 11. Эта диаграмма сильно упрощена и показывает только сигналы, используемые для чтения данных из внешнего устройства, подключенного в адресное пространство памяти. Использование отдельного задающего генератора для АЦП является предпочтительным, поскольку сигнал внутреннего генератора DSP-процессора может иметь высокий уровень помех и фазовый шум (jitter), который в процессе аналого-цифрового преобразования приведет к увеличению уровня шумов АЦП.

Тактовый импульс задающего генератора на входе "старт преобразования" (convert start) АЦП инициирует процесс преобразования входных данных (шаг N 1). По переднему фронту этого импульса внутренняя схема выборки-хранения АЦП переключается из режима выборки в режим хранения и таким образом начинается процесс преобразования. После выполнения преобразования на выходе АЦП выставляется строб преобразование выполнено (шаг N 2). Когда этот сигнал поступает на вход запроса прерывания DSP-процессора (IRQ), начинается процесс чтения данных из АЦП. Далее процессор выставляет на шине адрес периферийного устройства, инициировавшего запрос на прерывание (шаг N 3). В то же самое время процессор переводит в активное состояние сигнал доступа к памяти (DMS) (шаг N 4). Две внутренние шины адреса в процессоре ADSP-21XX (шина адреса памяти программ и шина адреса памяти данных) совместно используют внешнюю шину адреса, а две внутренние шины данных (шина данных памяти программ и шина данных памяти данных) совместно используют одну внешнюю шину данных. Сигналы выбора памяти начальной загрузки (BMS), выбора памяти данных (DMS), выбора памяти программ (PMS) и выбора памяти устройств ввода-вывода (IOMS) указывают, для какой памяти в данный момент используются внешние шины. Эти сигналы обычно используются для разрешения внешней дешифрации адреса, как показано на рис. 11. Выходной сигнал дешифратора адреса подается на вход chip select выбора периферийного устройства (шаг N 5).

Сигнал чтения памяти (memory read, RD) выставляется через промежуток времени tASR после активации сигнала DMS (шаг N 6). Чтобы полностью использовать преимущество высокой скорости DSP-процессора, сумма времени задержки дешифрации адреса и времени включения периферийного устройства после подачи сигнала выбора (chip select) не должна превышать время tASR. Сигнал чтения памяти (memory read, RD) остается активным (низкий логический уровень) в течение времени tRP. Этот сигнал используется для перевода в активное состояние параллельного выхода данных периферийного устройства (шаг N 7). Сигнал RD обычно подключается к соответствующему выводу периферийного устройства, называемому сигналом разрешения выхода или чтения (output enable или read). Восходящий (задний) фронт сигнала RD используется для ввода данных с шины в DSP-процессор (шаг N 8). После появления восходящего (заднего) фронта сигнала RD данные на шине должны удерживаться периферийным устройством в течение времени tRDH, называемого временем удержания данных. Для большинства процессоров семейства ADSP-21XX это время равно нулю.

Основные требования к временным параметрам периферийного устройства показаны на рис. 11. Все значения даны для процессора ADSP-2189M, работающего на тактовой частоте 75 МГц.

Рис 11. Подключение АЦП.

Процессор ADSP-2189M способен эффективно взаимодействовать с медленными периферийными устройствами при помощи имеющихся средств программирования длительности состояния ожидания. Имеется три специальных регистра для управления процессом ожидания: для памяти начальной загрузки, для памяти программ и для памяти данных и пространства ввода-вывода. Программист может задать от 0 до 15 тактов ожидания для каждого параллельного интерфейса памяти. Каждый такт ожидания увеличивает время доступа к внешней памяти на величину, равную по длительности одному такту генератора тактовых импульсов процессора (13.3 нс для процессора ADSP-2189M, работающего на тактовой частоте 75 МГц). В рассматриваемом примере сигналы адрес памяти данных, DMS и RD удерживаются неизменными в течение дополнительного времени, определяемого продолжительностью тактов ожидания. Микросхемы AD7854/AD7854L – это 12-разрядные АЦП, работающие с частотой отсчетов 100 или 200 кГц, которые имеют параллельный интерфейс. Эти АЦП работают от однополярного источника питания с напряжением от +3 В до +5.5 В и потребляют порядка 5.5 мВт (AD7854L при питании +3 В). Автоматическое переключение микросхемы в энергосберегающий режим после выполнения преобразования снижает потребляемую мощность до 650 мкВт. Функциональная схема AD7854/AD7854L показана на рис. 7.6. ИС AD7854/AD7854L реализует технологию преобразования методом последовательного приближения с применением ЦАП с перераспределением зарядов (ЦАП на переключаемых конденсаторах). Наличие режима калибровки позволяет избавиться от погрешности смещения и погрешности коэффициента усиления. Ключевые временные характеристики параллельного интерфейса между AD7854/AD7854L и ADSP-2189M показаны на рис. 12. Характеристики процессора ADSP-2189M приведены для тактовой частоты равной 75 МГц. Исследование временных соотношений, приведенных на рис 7.7, показывает, что для синхронизации работы двух устройств необходимо введение пяти тактов ожидания для процессора ADSP-2189M. Это увеличивает tRDD до 68.15 нс, что превышает минимальное время доступа к АЦП AD7854/AD7854L (t8 = 50 нс минимум). Длительность импульса чтения - tRP по той же причине увеличивается до 70.15 нс, что позволяет удовлетворить требование к длительности строба чтения (t7 = 70 нс минимум). Если периферийное устройство, включенное в адресное пространство памяти, не обладает чрезвычайно малым временем доступа, то использование режима ожидания совершенно необходимо для организации интерфейса с этим устройством, будь то АЦП, ЦАП или внешняя память.

|

Главная

Главная

Схемы

Схемы

Студентам

Студентам

Программы

Программы

Поиск

Поиск

Top50

Top50

Главная

Главная

Схемы

Схемы

Студентам

Студентам

Программы

Программы

Поиск

Поиск

Top50

Top50