Студентам > Курсовые > Разработка микропроцессорного устройства цифрового фильтра

Разработка микропроцессорного устройства цифрового фильтраСтраница: 2/6

2.2 МИКРОПРОЦЕССОРЫ КОМПАНИИ MOTOROLA

Сигнальные

микропроцессоры компании Motorola. Подразделяются на

семейства 16- и 24-разрядных микропроцессоров с фиксированной точкой – DSP – 560xx, - 561xx,

- 563xx, -566xx, 568xx и микропроцессоры с плавающей точкой – DSP

– 960xx.

Рассмотрим 24-х

разрядные микропроцессоры с фиксированной точкой семейства DSP

560xx. Эти микропроцессоры являются первыми представителями сигнальных

микропроцессоров компании Motorola. Архитектура

микропроцессоров ориентирована на максимизацию пропускной способности в

приложениях DSP с интенсивным обменом данными. Это

обеспечивается благодаря расширяемой архитектуре со сложной встроенной

периферией и универсальной подсистеме ввода/вывода. Данные свойства, а также

низкое энергопотребление минимизируют сложность, стоимость и сроки разработки

прикладных систем на базе микропроцессоров DSP56000/DSP56001.

Микропроцессоры

работают на частоте 33МГц и обеспечивают производительность около 16 MIPS, что позволяет выполнять быстрое преобразование Фурье по

1024 отсчетам за 3,23мс.

Дальнейшее развитие

семейства микропроцессоров осуществляется в рамках концепции процессорного

ядра, общего для всех представителей семейства, в состав которого входят

24-разрядные микропроцессоры с фиксированной точкой.

Процессоры данного

семейства характеризуются высокой пропускной способностью, расширенной

разрядностью, обеспечивающей высокую точность вычисления и широким динамическим

диапазоном обрабатываемых данных, поддержкой энергосберегающего режима работы.

Представители семейства отличаются друг от друга конфигурациями памяти и

периферийными устройствами.

2.3 МИКРОПРОЦЕССОРЫ КОМПАНИИ TEXAS INSTRUMENTS

Сигнальные

микропроцессоры компании Texas Instruments разделяются на два класса: это процессоры для

обработки чисел с фиксированной точкой и процессоры для обработки чисел с

плавающей точкой. Первый класс представлен тремя семействами процессоров,

базовыми моделями которых являются соответственно TMS320.10,

.20, .50. Второй класс включает процессоры TMS320.30, . 40, TMS320С80, которые поддерживают операции с плавающей точкой и представляют собой

мультипроцессорную систему, выполненную в одном кристалле, а семейство TMS320C6x

включает процессоры как с фиксированной, так и с плавающей точкой.

Процессоры старших

поколений одного семейства наследует основные архитектурные особенности и

совместимы “снизу вверх” по системе команд (чего нельзя сказать

о процессорах, входящих в разные семейства).

Перечислим

некоторые микропроцессоры, оптимально подходящие для нашей системы.

1.Микропроцессоры семейства TMS320C1x

Первый

процесор семейства – TMS320C10

был выпущен в 1982г. и благодаря ряду удачных технических решений получил

широкую распространенность.

В основу

микропроцессоров данного семейства положена модифицированная Гарвардская

архитектура, отличием которой от традиционной Гарвардской архитектуры является

возможность обмена данными между памятью программ и памятью данных, что

повышает гибкость устройства.

TMS320C10 является 16-разрядным

процессором. Его адресное пространство составляет 4K

16-разрядных слов памяти данных. Длительность такта процессора составляет

160-200 нс.

Арифметические

функции в процессоре реализованы аппаратно. Он имеет аппаратные умножители,

устройство сдвига, аппаратную поддержку автоинкремента/декремента адресных

регистров данных.

С внешними

устройствами процессор взаимодействует через 8 16-разрядных портов

ввода/вывода. Предусмотрена возможность внешнего прерывания.

Остальные

микропроцессоры данного семейства имеют аналогичную архитектуру и отличаются

длительностью командного такта, конфигурацией памяти, наличием (или

отсутствием) дополнительных периферийных устройств.

2.Микропроцессоры

семейства TMS320C2x.

Микропроцессоры

семейства TMS320C2x имеют анлогичную

архитектуру, но обладают повышенной производительностью и более широкими

функциональными возможностями. Все процессоры семейства поколения могут

использовать по 64K слов памяти программ и

данных, имеют 16 16-разрядных портов ввода/вывода и последовательный порт.

Процессоры

семейства TMS320C2x имеют возможность

использования внешнего контроллера ПДП. Умножитель микропроцессоров, помимо

операций умножения, позволяет выполнять за один такт возведение в квадрат. В

процессоры включена аппаратная поддержка кратного выполнения команды,

реализован режим двоичной инверсно-косвенной адресации, предназначенный для

эффективной реализации быстрого преобразования Фурье.

2.4 ОБОСНОВАНИЕ ВЫБРАННОГО ВАРИАНТА

После

длительного обзора микропроцесорных устройств, возникла задача выбора наиболее

подходящего микропроцессора. Решение данной задачи было найдено при

рассмотрении микропроцессоров компании Microchip.

Для реализации проекта было принято решение использовать микропроцессор

компании Microchip PIC16C711. Приведем преимущества использования данного микропроцессора

в курсовой работе, а также общие его характеристики.

PIC16C711 это дешевый, высокопроизводительный, изготовленный по

КМОП технологии 8-битный микроконтроллер. В основу процессора положена RISC архитектура, он имеет улучшенные характеристики ядра,

внутренние и внешние прерывания. Устройство имеет два двунаправленных порта

ввода/вывода, один из которых может быть использован как вход для

аналого-цифрового преобразования, другой - как выход для ЦАП. Тактовая частота

составляет 20MHz.

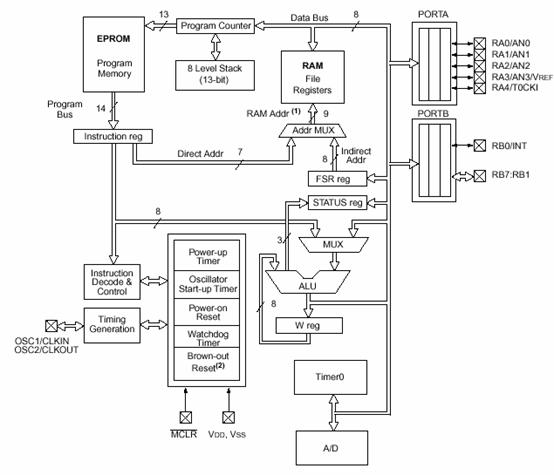

На рисунке 2.1

представлена структурная схема PIC16C711.

Перечислим основные элементы схемы: АЛУ (ALU), где

выполняются простейшие арифметические операции, а также логические операции;

аккумулятор (W), где хранятся данные результатов вычислений; регистр состояния,

в котором хранятся флаги результатов операций, а также биты выбора банка

памяти; регистр косвенной адресации (FSR), через

который непрямым образом можно обращаться к ОЗУ; память (RAM),

организованная 8-битными специальными регистрами и регистрами общего назначения,

рабочая область пользователя составляет 68x8; 13-битный

счетчик команд (Program Counter), младшие 8 бит приходят из регистра PCL, старшие 5 из регистра PCLATH;

ППЗУ (EPROM), составляет 1K 14-

битных ячеек памяти; стек 8-ми уровневый, длина слова 13-бит, во время

прерывания содержимое счетчика команд сохраняется в стек автоматически; два

двунаправленных 8-битных порта А и В; 4-х канальный 8-битный АЦП (A/D); счетчик Timer0.

Рис.

2.1 – Структурная схема PIC16C711

К сожалению устройство не имеет внутреннего ЦАП. ЦАП будет внешним, его

вход будет подсоединен к порту В. Применение внешнего ЦАП не ухудшит работу

цифрового фильтра и не усложнит его структуру, так как ЦАП не нужно

синхронизировать с временем выполнения программы, в отличие от АЦП.

Выбранный вариант технического решения полностью удовлетворяет

техническому заданию. Микроконтроллер + внешний ЦАП позволяют создать гибкую,

высокопроизводительную систему, удовлетворяющую требованиям микроминиатюрности,

быстродействия, качества и простоты исполнения. Сравнивая данный

микроконтроллер с большинством современных микроконтроллеров, можно сказать,

что он обладает сравнительно низкой стоимостью и доступностью на рынке Украины.

В современных системах обработки сигналов требуется высокая разрядность шины

данных и АЦП для увеличения точности вычислений, также для этих целей

необходимо, чтобы АЛУ могло вычислять операции с плавающей точкой. Выбранный

микроконтроллер не имеет данных свойств, но он благодаря своему быстродействию

и гибкости может вполне справиться с целью, поставленной в техническом задании

на курсовой проект.

Архитектура

процессора построена таким образом, что он способен выполнять команду за один

цикл, кроме операций условных и безусловных переходов. Это означает, что время

выполнения программы будет небольшим, и частота дискретизации АЦП будет

удовлетворять условию обработки сигналов качественной телефонии. Ассемблер

очень простой: пользователю необходимо выучить 35 команд. Последнее достоинство

позволяет снизить время на подготовку к выполнению проекта.

3 СИНТЕЗ ПРОЕКТИРУЕМОГО УСТРОЙСТВА

Структурная схема типа

реализации ЦФ приведена на рис.3.1. Параметры звеньев ЦФ следующие :

параметры звена  : :  ; ;

параметры звена  : :  ; ;

параметры звена  : :  . .

Рис.

3.1 – Структурная схема цифрового фильтра

Исходя из

этой структуры, а также коэффициентов, для каждого звена составим разностные

уравнения:

1) первое звено:

; ;

2) второе звено:

; ;

3) третье звено:

. .

Результирующее разностное

уравнение для цифрового фильтра будет иметь вид:

. .

4 РАЗРАБОТКА АЛГОРИТМА ПРОГРАММЫ

ПРОЕКТИРУЕМОГО УСТРОЙСТВА

Прежде чем

приступить к программированию устройства необходимо основательно изучить его

внутреннюю структуру и возможности ресурсов. Простейшая блок-схема

проектируемого устройства приведена на рисунке 4.1 В ней учтены конфигурация

портов и АЦП, вычисление разностного уравнения фильтра, результат вычислений

выдается на порт В.

Начало

Порт А –

вход

Порт В – Порт В –

выход

Запуск Запуск

АЦП АЦП

Вычисление

Вычисление

разностного

уравнения

Выдача

Выдача

Результата

На порт

В На порт

В

Рисунок 4.1 – блок-схема работы цифрового фильтра

Опираясь на данную блок схему, начнем более тщательное

рассмотрение вопроса.

Конфигурация портов и АЦП задается исходя из документации предлагаемой

производителем. Данная документация содержит примеры программ для настройки

портов и АЦП. Оговорим некоторые аспекты этих программ применительно к нашему

курсовому проекту. Контакты порта А зададим входами установкой битов в регистре

TRISA. Данное условие необходимо для осуществления

аналого-цифровой обработки сигнала. Контакты порта В зададим как выходные

сбросом битов в регистре TRISB. Для АЦП выберем канал

0, то есть вывод микропроцессора RA0. В PIC16C711 на одно преобразование АЦП

необходим минимальный интервал времени 10Тad, где Тad =1,6 мкс выбирается программно. Также

одной из важных частей программы запуска АЦП является организация разрешения

прерываний. рассмотрение вопроса.

Конфигурация портов и АЦП задается исходя из документации предлагаемой

производителем. Данная документация содержит примеры программ для настройки

портов и АЦП. Оговорим некоторые аспекты этих программ применительно к нашему

курсовому проекту. Контакты порта А зададим входами установкой битов в регистре

TRISA. Данное условие необходимо для осуществления

аналого-цифровой обработки сигнала. Контакты порта В зададим как выходные

сбросом битов в регистре TRISB. Для АЦП выберем канал

0, то есть вывод микропроцессора RA0. В PIC16C711 на одно преобразование АЦП

необходим минимальный интервал времени 10Тad, где Тad =1,6 мкс выбирается программно. Также

одной из важных частей программы запуска АЦП является организация разрешения

прерываний.

После конфигурации

портов и запуска АЦП необходимо приступить к выполнению программы вычисления

разностного уравнения, описывающего фильтр.

Просчитаем

количество переменных, входящих в уравнения. Это количество будет определять

необходимое число байт памяти. В нашем случае оно составляет 17. Нетрудно

заметить, что коэффициенты разностных уравнений подобраны таким образом, что

умножение переменной на них будет делением на 2,4,8…, а эта операция

выполняется путем сдвига регистра вправо. Для хранения промежуточных данных

сдвиговых операций и операций сложения нам понадобятся дополнительные ячейки

памяти в количестве 17. При начальном запуске программы или при сбросе

микропроцессорной системы все ячейки памяти необходимо сбросить в нуль.

На обработку данных

АЦП требуется, как указывалось ранее, время. Чтобы повысить эффективность и

качество системы, необходимо во время просчета АЦП, вместо простоя и ожидания

системой результата просчета, произвести вычисления без участия текущего значения

отсчета. Вычисления с участием текущего значения отсчета должны производиться

через время, равное 10Tad.

Результат

вычисления АЦП будет обрабатывать программа прерывания.

Исходя из всех

вышеприведенных соображений, составим окончательный алгоритм программы:

Начало

1

|

Главная

Главная

Схемы

Схемы

Студентам

Студентам

Программы

Программы

Поиск

Поиск

Top50

Top50

Главная

Главная

Схемы

Схемы

Студентам

Студентам

Программы

Программы

Поиск

Поиск

Top50

Top50