Студентам > Курсовые > Цифровой осциллограф

Цифровой осциллографСтраница: 2/9

Отличительной особенностью МК DS87C550 является перепроектированное ядро процессора, позволяющее исключить холостые такты и циклы памяти. В результате, каждая команда системы команд 8051 выполняется в три раза быстрее, чем стандартным МК, работающем на той же тактовой частоте. DS87C550 имеет максимальную тактовую частоту 33MHz, что эквивалентно работе стандартного МК с тактовой частотой до 99MHz.

МК C8051F120 выполняет 70% команд за 1 или 2 такта и обладает производительность до 100 MIPS на тактовой частоте 100МГц. Кроме того, он подходит по всем остальным параметрам для разрабатываемого устройства. Поэтому остановим свой выбор на нём.

АЦП должен быть сдвоенный и иметь частоту дискретизации 20 МГц. Такие АЦП выпускают многие производители. Так как Analog Devices выпускает качественные АЦП, то выберем из её продукции микросхему AD9288 c частотой преобразования 40 МГц.

3 Разработка принципиальной схемы и выбор электронных компонентов

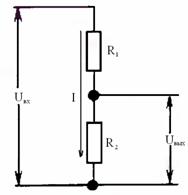

Как видно из структурной схемы аналогового блока нужно рассчитать аттенюаторы или делители напряжения для ослабления сигнала по амплитуде.

Рисунок 3.1 – Делитель напряжения

Предположим, что нагрузки нет, тогда по закону Ома  , а , а  . Для различных делителей будет меняться коэффициент ослабления . Для различных делителей будет меняться коэффициент ослабления  . .  , так как входное сопротивление входа осциллографа равно 1 МОм. В таблице 3.1 приведены результаты расчёта номиналов резисторов для делителей. , так как входное сопротивление входа осциллографа равно 1 МОм. В таблице 3.1 приведены результаты расчёта номиналов резисторов для делителей.

Таблица 3.1 – Номиналы резисторов для аттенюаторов |

|  , МОм , МОм

|  , МОм , МОм

| |

| 0.5 | 0.5 | |

| 0.8 | 0.2 | |

| 0.9 | 0.1 |

Резисторы на высоких частотах имеют паразитную ёмкость на подложку. Проволочные резисторы ведут себя хорошо на частотах до 50 кГц, углеродные резисторы используются на частотах до 1 МГц. Для данной схемы нужно использовать плёночные резисторы, которые имеют стабильные параметры на частотах до 100 МГц.

При работе в режиме постоянного напряжения сигнал подаётся сразу на делитель, а при работе с переменны напряжением для отсечения постоянных составляющих сигнала на вход ставится конденсатор. Конденсатор имеет комплексное сопротивление  . На частоте 10 МГц при С = 100 нФ . На частоте 10 МГц при С = 100 нФ  , что нам и требуется. , что нам и требуется.

Делители должны отключаться и подключаться к цепи по отдельности. Для этого будем использовать аналоговые ключи ADG201, обладающие сопротивлением 60 Ом в открытом состоянии и размахом напряжения аналогового входа  . Таким образом, коэффициент деления делителей не будет искажаться [2]. . Таким образом, коэффициент деления делителей не будет искажаться [2].

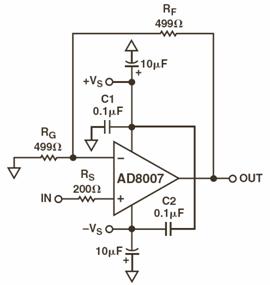

Для усиления сигнала будем использовать сдвоенный ОУ AD8008. ОУ имеет полосу пропускания по уровню -3 дБ равную 600 МГц при коэффициенте усиления  и диапазон напряжения на входе равный и диапазон напряжения на входе равный  . .

На рисунки 3.2 показана рекомендуемая производителем схема включения [3].

Рисунок 3.2 – Схема включения ОУ

Как известно при не инвертирующем включении идеального ОУ, его коэффициент усиления определяется простой формулой:  . Для задания коэффициента усиления . Для задания коэффициента усиления  в документации рекомендуется использовать следующие номиналы резисторов в: в документации рекомендуется использовать следующие номиналы резисторов в:  . Так как ключ включённый в цепь обратной связи ОУ имеет сопротивление в открытом состоянии 60 Ом, номинал . Так как ключ включённый в цепь обратной связи ОУ имеет сопротивление в открытом состоянии 60 Ом, номинал  . .

Для фильтрации ВЧ помех в цепи питания микросхем включаем конденсаторы.

На рисунке 3.3 представлена схема аналогового блока.

Выбранный АЦП имеет дифференциальные аналоговые входы. Для преобразования однопроводного сигнала в дифференциальный производитель рекомендует использовать ВЧ трансформатор ADT1-1WT, который имеет сопротивление 75 Ом и полосу пропускания 800 МГц [4]. Трансформатор не пропускает постоянный ток, поэтому для измерения постоянного напряжения будем использовать встроенный в микроконтроллер АЦП.

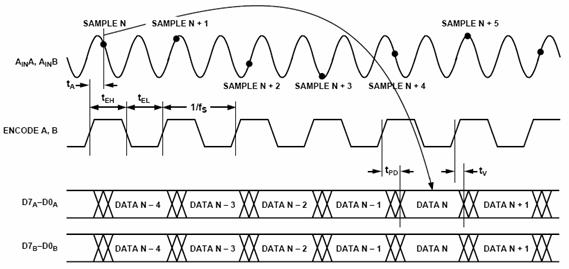

Через состояние входов S1 и S2 задаётся режим вывода данных на цифровые выходы D7-D0. При S1=1, S2=0 (нормальный режим) данные на цифровые выходы канала A и B выводятся одновременно, как показано на рисунке 3.4.

Рисунок 3.4 – Временные диаграммы для нормального режима работы АЦП  Рисунок 3.3 – Принципиальная схема аналогового блока Рисунок 3.3 – Принципиальная схема аналогового блока

АЦП имеет встроенный источник опорного напряжения (ИОН) напряжением 1.25 В, который подключен к выводу REFOUT. Ко входам REFINA и REFINB можно подключить внешний ИОН. Мы будем использовать встроенный источник, поэтому эти выводы не используются.

При подаче высокого уровня на вход DFS (Data Format Output) данные выводятся в дополнительном коде, а при низком уровня – в прямом коде.

На вход ENCA и ENCB подадим тактовый сигнал от МК для запуска процесса преобразования. На рисунке 3.5 изображена схема включения АЦП.

Порт P4 и P5 микроконтроллера подключены к цифровым выходам канала A и B АЦП соответственно.

Порт P0 используется для вывода сигнала тактирования АЦП. Порт P3 - для подачи сигналов управления на ЖКД.

Порт P1 – используется для вывода данных на ЖКД.

Вывод VDD – напряжение питания цифровой части МК, DGND – земля цифровой части МК. Вывод AV+ – напряжение питания аналоговой части МК, DGND – земля аналоговой части МК [5].

TMS, TCK, TDI, TDO – выводы через которые производится загрузка и отладка программы. Они соединены c выводами JTAG интерфейса.

|

Главная

Главная

Схемы

Схемы

Студентам

Студентам

Программы

Программы

Поиск

Поиск

Top50

Top50

Главная

Главная

Схемы

Схемы

Студентам

Студентам

Программы

Программы

Поиск

Поиск

Top50

Top50