Студентам > Рефераты > Триггеры

ТриггерыСтраница: 2/3

Нетрудно понять, что для данного триггера комбинация входных сигналов S=0, R=0 является запрещенной, а комбинация S=1, R=1 не меняет его предыдущего состояния.

3 Тактируемые триггеры

На входы логического элемента или устройства сигналы не всегда поступают одновременно, так как перед этим они могут проходить через разное число элементов, не обладающих к тому же одинаковой задержкой. Это явление описывают как состязания или гонки сигналов. В результате в течение некоторого времени на входах создается непредвиденная ситуация: новые значения одних сигналов сочетаются с предыдущими значениями других, что может привести к ложному срабатыванию элемента (устройства). Последствия гонок можно устранить временным стробированием, когда на элемент, кроме информационных сигналов, подаются тактирующие (синхронизирующие) импульсы, к моменту прихода которых информационные сигналы заведомо успевают установиться на входах.

Тактируемый триггер, кроме информационных входов, имеет синхронизирующий (тактирующий, тактовый) вход; сигналы на информационных входах воздействуют на такой триггер только с поступлением сигнала на синхронизирующий вход.

3.1. Структуры триггеров |

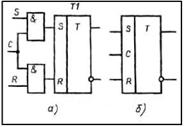

Рис.5. |

Тактируемый RS-триггер (рис.5,а). Схема такого триггера (собранного на элементах ИЛИ-НЕ) содержит асинхронный RS-триггер T1 и два конъюнктура входной логики. Последние передают переключающую логическую 1 с информационного S- или R-входа на соответствующие входы Т1 только при наличии на синхронизирующем входе С логической 1. При С=0 информация с S- и R-входов на триггер Т1 не передается.

Рассматриваемый триггер может быть выполнен и на запоминающей ячейке, реализованной на элементах И-НЕ.

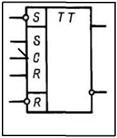

Условное изображение тактируемого триггера приведено на рис. 5,б. В тексте тактируемый RS-триггер сокращенно обозначают как RSC-триггер.

Синхронизирующие входы триггера могут быть статическими и динамическими. Статический вход не теряет своего управляющего действия, пока на нем присутствует тактовый (синхро) импульс. Такие входы имеет триггер, изображенный на рис. 5,а. В присутствии тактового импульса эти триггеры будут менять свое состояние при каждой смене комбинаций логических потенциалов на входах S и R. Динамический синхровход воздействует на состояние выходов триггера в момент своего появления (передним фронтом) или окончания (задним фронтом). |

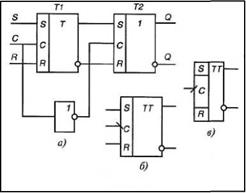

Рис.6. |

Двухступенчатый тактируемый RS-триггер (рис.6,а). Каждая ступень такого триггера представляет собой тактируемый RS-триггер. При появлении на входе С логической 1 триггер Т1 воспринимает информацию на входах S и R, определяющую его состояние. В это время на С-входе триггера Т2 за счет инвертора — логический 0, и информация с выходов Т1 не воздействует на Т2. В момент окончания действия логической 1 на входе С (С=0) на выходе инвертора появляется логическая 1, разрешающая перезапись в Т2 информации из Т1. Таким образом, в первую ступень информация с входов S и R записывается с поступлением тактового импульса, т. е. по его переднему фронту; состояние первой ступени передается второй с окончанием тактового импульса, т. е. по его срезу. По этому внешнему проявлению тактирующего импульса C-вход описанного триггера можно рассматривать как динамический.

Условное изображение двухступенчатого RS-триггера, в котором переключение выходов второй ступени триггера происходит перепадом входного сигнала из 1 в 0 (перепадом 1 / 0), приведено на рис.6,б. Условное изображение триггера с C-входом, переключающим триггер перепадом 0/1, приведено на рис. 6, в.

Тактируемый (синхронный) триггер обычно имеет дополнительные асинхронные входы, но которым он вне зависимости от сигнала на тактовом входе переключается в состояние 1 (по входу S) или в 0 (по входу R). Такие входы называют не тактируемыми или асинхронными. Логические потенциалы на них воздействуют на запоминающие ячейки триггера непосредственно (для чего эти ячейки триггера выполнены на трехвходовых элементах), минуя входную логику.

Условное изображение двухступенчатого триггера с инверсными асинхронными входами приведено на рис. 7.

|

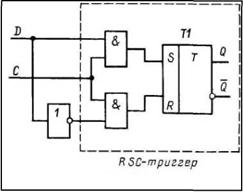

Рис.8. | |

Рис.7. |

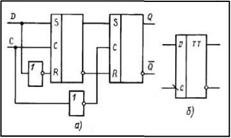

D -триггер (триггер задержки) – рис. 8 . D-триггер имеет один информационный D-вход и тактовый С-вход. Он состоит из синхронного RSC-триггера, дополненного инвертором. При С=1 потенциал D-входа передается на S-вход триггера T1 (S=D), а на входе R устанавливается потенциал R= : сигналы на входах оказываются взаимно инвертированными. Это приводит к тому, что любой сигнал на входе D создает на S- и R-входах комбинацию (S=1, R=0 или S=0, R=1), способную переключить триггер в состояние Q=S=D. Таким образом, при С=1 D-триггер является повторителем: на выходе Q повторяется потенциал входа D. Однако это повторение начинается только с поступлением тактового импульса на вход С, т. е. с задержкой относительно сменившегося потенциала на D-входе. При С=0 триггер Т1 и D-вход разобщены, поэтому S=0 и триггер хранит информацию, поступившую с D-входа при С = 1. Так как в D - триггере информация поступает по одной линии – на D-вход, то явление гонок не проявляется. Поэтому в быстродействующих цифровых устройствах используют D-триггеры. : сигналы на входах оказываются взаимно инвертированными. Это приводит к тому, что любой сигнал на входе D создает на S- и R-входах комбинацию (S=1, R=0 или S=0, R=1), способную переключить триггер в состояние Q=S=D. Таким образом, при С=1 D-триггер является повторителем: на выходе Q повторяется потенциал входа D. Однако это повторение начинается только с поступлением тактового импульса на вход С, т. е. с задержкой относительно сменившегося потенциала на D-входе. При С=0 триггер Т1 и D-вход разобщены, поэтому S=0 и триггер хранит информацию, поступившую с D-входа при С = 1. Так как в D - триггере информация поступает по одной линии – на D-вход, то явление гонок не проявляется. Поэтому в быстродействующих цифровых устройствах используют D-триггеры. |

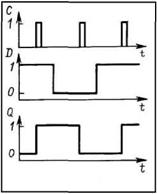

Рис.9. |

На рис.9 приведены временные диаграммы D-триггера. Выход Q повторяет состояние D-входа с поступлением очередного тактового импульса на вход С, т. е. с задержкой. На рис.9 приведены временные диаграммы D-триггера. Выход Q повторяет состояние D-входа с поступлением очередного тактового импульса на вход С, т. е. с задержкой.

D-триггер можно выполнить двухступенчатым. При этом его первая ступень представляет собой одноступенчатый D-триггер, а вторая может быть синхронным RSC-триггером (рис. 10,а). Состояние D-входа передается первой ступени с приходом тактового импульса, т. е. по его переднему фронту; вторая ступень (триггер в целом) принимает состояние первой с окончанием тактового импульса, т. е. по его заднему фронту. Условное изображение двухтактного D-триггера, переключающегося перепадом 1/ 0 приведено на рис. 10,б.

|

Главная

Главная

Схемы

Схемы

Студентам

Студентам

Программы

Программы

Поиск

Поиск

Top50

Top50

Главная

Главная

Схемы

Схемы

Студентам

Студентам

Программы

Программы

Поиск

Поиск

Top50

Top50