Студентам > Рефераты > Проектирование АЛУ для сложения двоично-десятичных чисел

Проектирование АЛУ для сложения двоично-десятичных чиселСтраница: 2/3

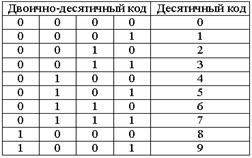

Иногда бывает удобно хранить числа в памяти процессора в десятичном виде (Например, для вывода на экран дисплея). Для записи таких чисел используются двоично-десятичные коды. Для записи одного десятичного разряда используется четыре двоичных бита. Эти четыре бита называются тетрадой. Иногда встречается название, пришедшее из англоязычной литературы: нибл. При помощи четырех бит можно закодировать шестнадцать цифр. Лишние комбинации в двоично-десятичном коде являются запрещенными. Таблица соответствия двоично-десятичного кода и десятичных цифр приведена в таблице 1.

Таблица 1.

Остальные комбинации двоичного кода в тетраде являются запрещенными. Запишем пример двоично-десятичного кода:

1258 = 0001 0010 0101 1000

589 = 0000 0101 1000 1001

Достаточно часто в памяти процессора для хранения одной десятичной цифры выделяется одна ячейка памяти (восьми, шестнадцати или тридцатидвухразрядная). Это делается для повышения скорости работы программы. Для того, чтобы отличить такой способ записи двоично-десятичного числа от стандартного, способ записи десятичного числа, как это показано в примере, называется упакованной формой двоично-десятичного числа.

1.3Суммирование двоично-десятичных чисел

Суммирование двоично-десятичных чисел можно производить по правилам обычной двоичной арифметики, а затем производить двоично-десятичную коррекцию. Двоично-десятичная коррекция заключается в проверке каждой тетрады на допустимые коды. Если в какой либо тетраде обнаруживается запрещенная комбинация , то это говорит о переполнении. В этом случае необходимо произвести двоично-десятичную коррекцию. Двоично-десятичная коррекция заключается в дополнительном суммировании числа шесть (число запрещенных комбинаций) с тетрадой, в которой произошло переполнение или произошёл перенос в старшую тетраду. Приведём два примера:

Каждое целое число занимает два байта (две ячейки) в памяти компьютера, т.е. 16 разрядов. При этом старший разряд отводится под знак числа. У положительных чисел в старшем разряде находится 0, а у отрицательных — 1. Таким образом, можно закодировать числа в диапазоне от —32 768 до 32 767. Отрицательные числа кодируются в дополнительном коде.

Правила создания дополнительного кода:

1) Все биты модуля двоичного числа инвертируются.

2) К полученному числу прибавляется 1.

Примеры:

3- 0000000000000011

- 3 - 11111111 11111101

9- 0000000000001001

-9- 11111111 11110111

32 767- 0111111111111111

—32 767- 10000000 00000001

—32 768- 10000000 00000000 2 Построение АЛУ

2.1 Построение функциональной и структурной схем АЛУ

АЛУ состроит из следующих функциональных блоков рис 6:

Блок ввода, включающий в себя клавиатуру с кнопками набора цифр, а также управляющие клавиши «=,+,- «Сброс»» и входные регистры;

Блок вычислений. В состав блока вычислений входят сумматоры, преобразователи дополнительного кода и схема коррекции;

Блок индикации, который состоит из дешифраторов, семисегментных индикаторов, а также схемы сравнения, состоящей из трёх компараторов.

Рисунок 6

Рассмотрим принцип работы устройства по функциональной схеме. На клавиатуре набирается число. В данном случае набираемое число не должно превышать двух знаков (максимамальное-99). Набираемое число поступает на регистр. В случае если число состоит из одного знака, то после нажатия управляющей клавиши «+» или «-» сигнал «выгружается» в блок вычислений на входы сумматора. Если же число состоит из двух знаков, в этом случае первая внесённая цифра последовательно передается в другой сумматор старшего разряда десятичного числа. Аналогичным образом происходит ввод второго числа. После набора чисел, при нажатии клавиши «=» результат суммы поступает в схему коррекции блока вычислений, при необходимости корректируется, с последующей передачей сигнала в блок индикации, где происходит дешифрация числа из двоично-десятичного кода в десятичный. Необходимо обратить внимание на то, что при нажатии клавиши «-» происходит преобразование числа в обратный код. Одновременно происходит сравнение введённых чисел. В том случае, если первое число меньше другого формируется знак минус на индикаторе с помощью схемы сравнения.

2.2 Описание работы принципиальной схемы

В момент включения устройства (рис приложение 1) либо нажатии клавиши «Сброс», происходит сброс всех регистров, при этом триггер Т2 (микросхема DD12) находится в нулевом состоянии. Двоичный код введённого числа с клавиатуры поступает на вход регистра RG1 (микросхема DD1). Одновременно сигнал с входа регистра поступает через логический элемент ИЛИ на вход ключа, (элемента И). Так как триггер Т2 находится в нулевом состоянии, то полученный сигнал поступает на разрешающие входы регистра RG1, после чего данные передаются на выход регистра. Регистр RG2 (микросхема DD1) подключён последовательно регистру RG1. Код с выхода RG1 подаётся на вход RG2, который в свою очередь находится в закрытом состоянии. Открытия регистра RG2 происходит в момент следующего нажатия клавиши. В этом случае данные из регистра RG1 перегружаются в регистр RG2 – в старший разряд десятичного числа, а вновь введённое число помещается на место предыдущего – в младший. После нажатия клавиши «+»или « - », триггер Т2 переключается в единичное состояние. В этом случае регистр RG1 закрыт, а ввод осуществляется аналогичным образом в регистры RG3 и RG4 (микросхема DD2). Необходимо обратить внимание на то, что при нажатии клавиши « - » происходит переключение триггера Т4 (микросхема DD12) в единичное состояние, после чего данные на выходе регистров RG3 и RG4 преобразуются в дополнительный код. Далее, коды поступают на входы сумматоров SM1, SM2 (микросхемы DD3, DD4). Одновременно информация с выходов регистров RG1- RG4 поступает на компараторы = =1-= =3 (микросхемы DD7, DD8, DD9). Где происходит сравнение чисел и формирования знака « - » в случае отрицательного результата. После суммирования чисел производится коррекция полученного результата, т.е. в случае появления запрещенных комбинаций происходит сложение переполненных разрядов с числом 6. Данная коррекция выполняется на сумматорах SM3, SM4 (микросхемы DD5, DD6). Отображение вводимых чисел, а также результата вычисления выполняется с помощью дешифраторов DC1 и DC2 (микросхемы DD10, DD11). Вначале, когда триггер Т2 находится в нулевом состоянии происходит отображение первого вводимого числа. Так, как параллельно управлению регистрами RG1и RG2, триггер Т2 производит управление дешифраторами. Управление осуществляется путем подачи инвертированного нулевого сигнала с триггера Т2 на управляющий вход дешифратора. В этот момент, код, имеющийся на выходах регистров RG1и RG2, помещается в дешифратор, где происходит его преобразование с последующей передачей на индикаторы HL1, HL2. Как только нажата клавиша «+» или «-», происходит блокировка данных с регистров первого числа, из-за того, что триггер Т2 становится в единичное состояние. Дешифратор готовится к отображению второго вводимого числа. Индикация второго числа осуществляется аналогично первому. Вывод результата на индикаторы происходит после нажатия клавиши «=». В этом случае блокируются, выходы регистров RG3 и RG4 и на вход дешифраторов поступает выходной сигнал с сумматоров SM3 и SM4. Вывод третий цифры на индикаторе, в случае переполнения второго двоично-десятичного разряда производится с выхода переноса в следующий разряд сумматоров SM3 и SM4. В этом случае сигнал с выходов Cn+1 предаются на соответствующие ячейки третьего индикатора HL3.

|

Главная

Главная

Схемы

Схемы

Студентам

Студентам

Программы

Программы

Поиск

Поиск

Top50

Top50

Главная

Главная

Схемы

Схемы

Студентам

Студентам

Программы

Программы

Поиск

Поиск

Top50

Top50