Студентам > Курсовые > Разработка МПУ для сушильной печи

Разработка МПУ для сушильной печиСтраница: 2/4

– какой-либо из регистров общего назначения (B, C, D, E, H, L);

– 16-разрядный указатель стека;

– 16-разрядный счётчик команд;

– 8-разрядный буфер адреса/данных.

Арифметико-логическое устройство загружается двумя 8-разрядными регистрами (аккумулятором и регистром временного хранения), как в типовом МП.

Регистр состояний содержит пять индикаторов состояния вместо двух, как это было в типовом МП.

Регистр команд связан с дешифратором, который определяет текущую команду, требуемую микропрограмму или следующий машинный цикл, а затем информирует схему управления и синхронизации о последовательности действий. Эта схема координирует действия МП и периферии.

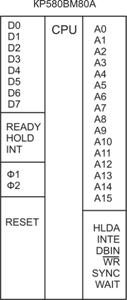

2.1. Описание микропроцессора КР580ВМ80А.

Этот микропроцессор представляет собой 8-разрядный процессор, в котором совмещены операционные и управляющие устройства. Управляющая память недоступна пользователю, в ней уже в процессе изготовления БИС записываются микропрограммы операций. Таким образом, предусматривается использование некоторой фиксированной системы команд, в которую пользователь не может внести изменений. В связи с этим данный микропроцессор относится к числу немикропрограммируемых. Этот микропроцессор представляет собой 8-разрядный процессор, в котором совмещены операционные и управляющие устройства. Управляющая память недоступна пользователю, в ней уже в процессе изготовления БИС записываются микропрограммы операций. Таким образом, предусматривается использование некоторой фиксированной системы команд, в которую пользователь не может внести изменений. В связи с этим данный микропроцессор относится к числу немикропрограммируемых.

КР580ВМ80А Выполнение каждой команды производится микропроцессором в строго определенной последовательности действий, которая определяется кодом команды и синхронизируется сигналами Ф1 и Ф2 тактового генератора. Для формирования управляющих сигналов искусственно мультиплексируют шину данных, то есть в начале каждого машинного цикла на шину данных микропроцессор выставляет 8 управляющих сигналов, называемых байтом состояния. Байт состояния указывает, какой из машинных циклов выполняется в текущий момент, то есть к какому из внешних устройств происходит обращение. Байт состояния выставляется на шину данных по переднему фронту сигнала Ф2 в первом такте и снимается с шины данных по переднему фронту Ф2 во втором такте. Для того, чтобы показать, что идет процесс передачи байта состояния, используется выход SYNC микропроцессора: при выводе байта состояния на выходе SYNC=1. Сигнал SYNC=1 позволяет выделить байт состояния из информации передаваемой по шине данных. Байт состояния выдаётся на шину данных в интервале SYNC=1, а используется на протяжении всего машинного цикла. Поэтому байт состояния запоминается в специальном регистре слова - состояния. Запись производится с использованием сигналов SYNC=1 и Ф2=1. Дешифратор преобразует

байт состояния требуемые для текущего машинного цикла системные управляющие сигналы. При формировании этих управляющих сигналов для согласования блоков МПС по временным характеристикам используются выходные сигналы микропроцессора DBIN и WR. Регистр слова-состояния и дешифратор, обеспечивающие формирование системных управляющих сигналов, называются системным контроллером.

Назначение выводов микропроцессора. | Сигнал | Название | |

D0 – D8 |

Двунаправленная 8-разрядная шина данных, которая выполняет: передачу управляющего слова; обмен данными между регистрами микропроцессора и блоками МПС | |

A0 – A15 |

Направленная от микропроцессора 16 - разрядная шина, которая выполняет: передачу адреса ячейки памяти при обращении памяти; передачу адреса внешнего устройства. В этом случае 8 – разрядный адрес УВВ появляется на выводах А0 – А7 и дублируются на линиях А8 – А15 | | Сигналы управления шиной данных | |

DBIN |

Выходной сигнал "Прием". Если DBIN=1, то шина данных настроена на прием данных в микропроцессор из памяти или УВВ. Если DBIN=0, то шина данных настроена на вывод информации из микропроцессора. | |

WR |

Выходной сигнал "Выдача данных". Если WR=0, то микропроцессор зафиксировал на шине данных 8-разрядный код, который должен быть воспринят памятью или УВВ. | | Сигналы управления вводом - выводом | |

READY |

Входной сигнал "Готовность" от УВВ или памяти. Если READY=1, то УВВ или память готовы к обмену данными с микропроцессором. Если READY=0, то УВВ или память не готовы к обмену данными с микропроцессором. В этом случае микропроцессор входит в режим "Ожидание". | |

WAIT |

Выходной сигнал "Ожидание". Если WAIT=1, то микропроцессор находится в режиме "Ожидание". | |

INT |

Входной сигнал "Запрос прерывания" от УВВ. Если INT=1, следовательно, одному из УВВ требуется обслуживание. | |

INTE |

Выходной сигнал "Разрешения прерывания". Этот сигнал информирует УВВ о возможности или невозможности обслуживания микропроцессором запросов на прерывание. Если INTE=1, то прерывания разрешены. Если INTE=0, то прерывания запрещены. | |

HOLD |

Входной сигнал "Запрос захвата шин" от УВВ. Если HOLD=1, значит, одно из УВВ требует обмена по прямому доступу к памяти. | |

HLDA |

Выходной сигнал "Подтверждение захвата шин". Если HLDA=1, то микропроцессор отключился от системных шин и "отдал" их в распоряжение УВВ и памяти | | Сигналы синхронизации | |

Ф1, Ф2 |

Входные сигналы от тактового генератора. | |

SYNC |

Выходной сигнал "Синхронизация". Если SYNC=1, то на шину данных микропроцессор выставил восемь управляющих сигналов. | |

RESET |

Входной сигнал "Сброс". Сигнал начальной установки микропроцессора. Если RESET=1 в течение 3-4 периодов тактовой частоты, то микропроцессор прекращает свою работу, обнуляет счетчик команд и бездействует. Как только RESET=0, микропроцессор начинает выполнять команду, записанную по адресу 0000Н. |

2.2. Описание генератора тактовых импульсов.

|

Главная

Главная

Схемы

Схемы

Студентам

Студентам

Программы

Программы

Поиск

Поиск

Top50

Top50

Главная

Главная

Схемы

Схемы

Студентам

Студентам

Программы

Программы

Поиск

Поиск

Top50

Top50