Студентам > Курсовые > Разработка цифрового таймера

Разработка цифрового таймераСтраница: 3/5

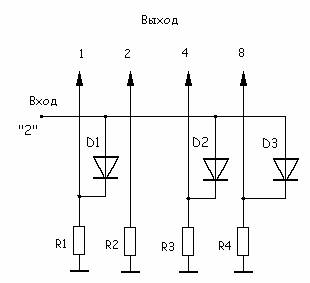

Рис.

При подаче положительного напряжения на вход “2” диоды открываются и на выходе

устанавливаются инверсные логические уровни 1101, соответствующие числу два.

Резисторы R1-R4 необходимы для

надежного открывания диодов, в случае если входное сопротивление

регистра-защелки окажется слишком велико.

Минимальное сопротивление этих резисторов выбирается исходя из максимального

допустимого тока через диоды. При этом учитывается то, что их сопротивление

должно быть в 5-6 раз больше чем сопротивление ограничительного резистора в

блоке клавиатуры.

Максимальное сопротивление резисторов ограничивается минимальным входным током

логических элементов ТТЛШ, при котором входной сигнал воспринимается как

логический ноль. Это сопротивление рекомендуется не более 3 кОм. Исходя из

этого было выбрано сопротивление R1-R4 2,7 кОм, а сопротивление ограничительного резистора в клавиатуре

– 470 Ом.

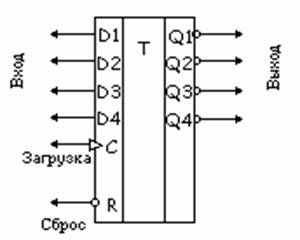

3) Регистр-защелка

Регистр-защелка должен обеспечивать запись

входных значений по сигналу от СУ и выдачу этих значений в инверсном коде.

Помимо этого он должен иметь вход обнуления. Количество разрядов регистра

должно быть не менее четырех. При всем многообразии возможные технических

решений наиболее экономичным является использование в качестве РЗ микросхемы

К555ТМ8, которая предназначена для построения параллельных регистров данных,

запускаемых перепадами тактовых импульсов. Микросхема расположена в

16-контактном корпусе и содержит набор D-триггеров, имеющих общие входы синхронного

сброса R и тактового запуска С._В микросхеме ТМ8 число триггеров четыре, у каждого есть прямые и инверсные выходы

Q. Цоколевка микросхемы показана на рис. .

Режимы работы триггеров микросхемы соответствуют табл. . Сброс всех триггеров в

состояние Qн = 0

произойдет, когда на вход асинхронного сброса R

будет подано напряжение низкого уровня. Входы C

и Dn при этом не действуют, их состояние

безразлично.

Информацию от параллельных входов данных

D1-D4 можно загрузить в триггеры микросхемы, если

на вход R подать напряжение высокого уровня, а на

тактовый вход С – положительный перепад импульса. При этом предварительно

установленные на каждом входе D напряжения высокого или низкого уровня

появятся на выходе Q.

Микросхема К555ТМ8 потребляет ток 18 мА,

максимальная тактовая частота составляет 35 МГц, время задержки распространения

сигнала сброса – 28 ns.

Рис.

Табл.

|

Режим

работы

|

вход

|

Выход

|

|

R

|

C

|

Dn

|

Qn

|

Qn

|

|

Сброс

|

0

|

Х

|

Х

|

0

|

1

|

|

Загрузка 1

|

1

|

0-1

|

1

|

1

|

0

|

|

Загрузка 0

|

1

|

0-1

|

0

|

0

|

1

|

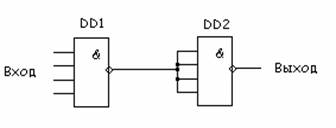

4) Детектор

нажатий

Как было сказано выше, в качестве детектора

нажатий используется логический элемент И с четырьмя входами. Поскольку в

серии К555 есть только элементы И–НЕ то придется использовать дополнительный

инвертор. Наиболее целесообразно в качестве ДН использовать микросхему К555ЛА1

– два логических элемента 4И–НЕ. Схема ДН, построенная на этой микросхеме

приведена на рис.

Один из элементов используется по своему

прямому назначению, а второй выступает в качестве детектора.

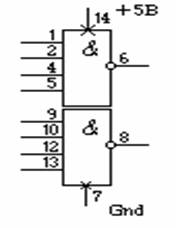

Рис.

Микросхема

потребляет ток 2,2 мА. Максимальная задержка распространения в одном ЛЭ – 15

ns. Цоколевка микросхемы показана на рис.

Рис.

5)

Дешифратор позиций загрузки

Согласно структурной схеме дешифратор позиций загрузки

на основании входного двухразрядного двоичного кода должен устанавливать

логический ноль на одном из четырех выходов. Кроме того он должен иметь два

инверсных входа стробирования, подключаемых к схеме управления и к детектору

нажатий. Наиболее подходящим решением в данном случае является использование в

качестве ДПЗ одного из дешифраторов ИМС К555ИД4.

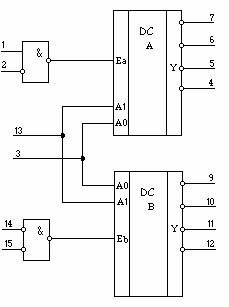

Микросхема К155ИД4 (рис. ) — два

дешифратора, принимающих двухразрядный код адреса А0, А1. Дешифратор

DC A имеет два

входа разрешения:

прямой Еа и инверсный Ёа, а дешифратор DC B —

только инверсные входы разрешения дешифрации

Еb.

Рис.

Если микросхема используется как демультиплексор, дешифратор

DC A может принимать по входам Еа и Еа как

прямой, так и инверсный адресные коды. Состояния для обоих дешифраторов как при дешифрации кода А0, А1,

так и при демультиплексировании по адресу А0, А1 сведены в табл.

Табл.

Микросхема К555ИД4 потребляет ток 10 мА. Время задержки распространения сигнала

от адресного входа А к выходу Y составляет 32

ns, время

распространения от входа разрешения Е к выходу Y не

превышает 30 ns для обоих вариантов исполнения.

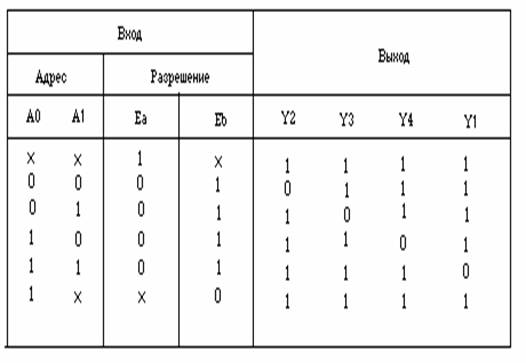

Принципиальная

схема ДПЗ построенного на К555ИД4 приведена на рис.

Рис.

На входы А0 и А1 подается двоичное число

произведенных нажатий клавиш от счетчика нажатий, а на входы Е1 и Е2 – сигналы

разрешения от детектора нажатий и схемы управления. Выходы 0,1,2,3 подключаются

к соответствующим разрядам счетчика выдержки времени.

Блоки отсчета выдержки

_______________________________________________________

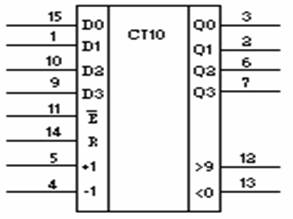

1) Счетчик выдержки

времени

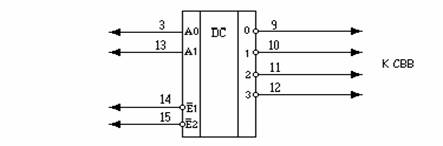

Счетчик выдержки времени является одним из основных узлов данного устройства.

Он предназначен для подсчета количества поступающих от задающего генератора

импульсов. Принципиальная схема счетчика приведена на рис. Счетчик работает в

режиме вычитания – из заданного первоначально количества импульсов с приходом

очередного импульса вычитается единица. Когда счетчик полностью обнулится, на

его выходе "<0" (МС DD1) появляется

логический ноль, который, воздействуя на БУИУ, отключит нагрузку. Загрузка

значений в счетчик производится параллельным способом, путем подачи

соответствующего двоичного значения на входы D0

- D4, и логического нуля на один из входов

разрешения загрузки Е.

Рис.

Тактовые импульсы подаются на счетный вход +1 микросхемы

DD4. Блок дешифраторов подключается к выводам

1-2-4-8 каждой из микросхем.

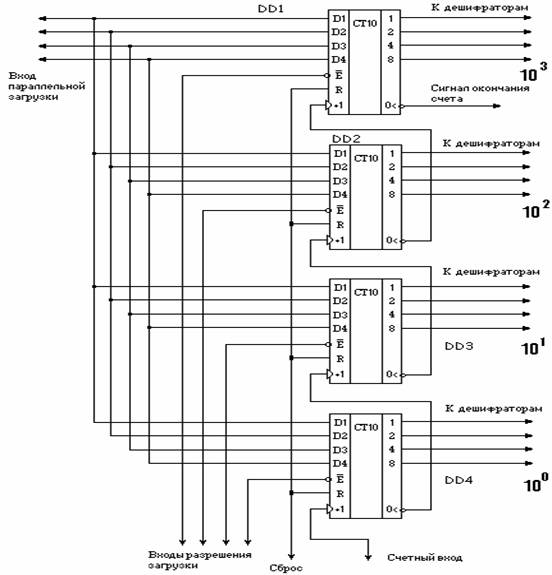

Для построения

счетчика была использована микросхема К555ИЕ6, что позволило обойтись всего

четырьмя микросхемами без каких либо дополнительных элементов. Цоколевка

микросхемы показана на рис.

Рис.

Микросхема представляет собой реверсивный двоично-десятичный счетчик. Импульсные тактовые входы для счета на увеличение +1 (вывод 5) и на

уменьшение -1 (вывод 4) в этой

микросхеме раздельные. Состояние счетчика

меняется по положительным перепадам тактовых импульсов от низкого уровня к

высокому на каждом из этих тактовых входов.

Для упрощения построения счетчиков с числом

разрядов, превышающих четыре, микросхема имеет выводы

окончания счета на увеличение (">9", вывод 12) и на уменьшение ("<0",

вывод 13). От этих выводов берутся

тактовые сигналы переноса и заема для последующего и от

предыдущего четырехразрядного

счетчика. Дополнительной логики при последовательном соединении этих счетчиков не требуется: выводы ">9" и

"<0" предыдущей

микросхемы присоединяются к выводам "+1" и "-1" последующей. По входам

разрешения параллельной загрузки РЕ и сброса R запрещается действие тактовой последовательности и даются

команды загрузки четырехразрядного кода в счетчик или его сброса.

|

Главная

Главная

Схемы

Схемы

Студентам

Студентам

Программы

Программы

Поиск

Поиск

Top50

Top50

Главная

Главная

Схемы

Схемы

Студентам

Студентам

Программы

Программы

Поиск

Поиск

Top50

Top50