Студентам > Дипломные работы > Разработка методики программного тестирования цифровых устройств

Разработка методики программного тестирования цифровых устройствСтраница: 2/3

Ниже приведена модель

управляющей схемы и результат ее тестирования:

u1 inva(2) up um 09 10

out1a out2a delay1 in_out

u2 anda(3,3) up um 10 03

out1a 09 out2a 03 03 09 10 4 5

+6 delay1 in_out

.model delay1 ugate

u3 dff(2) up um 04 05 03 01

02 07 08 09 10 delay source

Ugnr1 STIM (1,1)

+ up um

+03

+ source TIMESTEP =

10.00000E-9 IO_LEVEL=0

+ 0.000000C 0

+ LABEL = again

+ 1.000000C 1

+ 2.000000C 0

+ 3.000000C GOTO again -1

TIMES

uconst1 pullup(2)

$g_cd4000_vdd $g_cd4000_vss 04 01 in_out

uconst0 pulldn(1)

$g_cd4000_vdd $g_cd4000_vss 02 in_out

ur STIM (1,1)

+ $G_DPWR $G_DGND 05 source

TIMESTEP = 1.000000E-9 IO_LEVEL=0

+ 0.000000s 0

+ 2.000000E-9s 1

* uconst0 pulldn(1)

$g_cd4000_vdd $g_cd4000_vss S in_out

.model delay ueff

.model in_out uio(drvh=1e4

drvl=1e4)

.options digmntymx=2

.model source uio(drvh=50

drvl=50)

.probe

.tran 10ns 400ns

.end

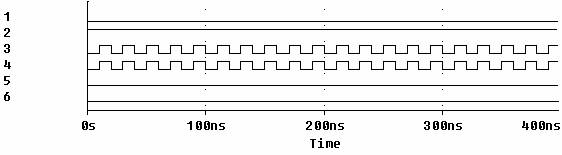

Результат тестирования

управляющей схемы приведен в приложении Г.

3.2.7 Создание модели формирователя пачек импульсов, входящего в состав цифрового

синхронизирующего устройства.

Тестирование модели формирователя пачек импульсов.

Основной

задачей формирователя пачек импульсов является форми-рование сигнала в состав

которого входят импульсы,

число которых задается управляющей схемой.

В основе формирователя

пачек импульсов лежит вычитающий счетчик СТ1, построенный на Т-триггерах.

В библиотеке PSpice нет модели Т-триггера, так как данный тип триггера может

быть реализован на основе D-триггера. Данная реализация производится путем

соединения инвертирующего выхода D-триггера

с его D-входом. Таким образом получается триггер с

одним входом и состояние триггера меняется с уровнем сигнала на его входе.

Ниже приведена модель

Т-триггера:

u1 dff(1) up um R S c inv out

inv delay source

Ugnr1 STIM (1,1) up um c source

TIMESTEP = 10.00000E-9 IO_LEVEL=0

+ 0.000000C 0

+ LABEL = again

+ 1.000000C 1

+ 2.000000C 0

+ 3.000000C GOTO again -1

TIMES

uconst1 pullup(1)

$g_cd4000_vdd $g_cd4000_vss S source

ur STIM (1,1) $G_DPWR $G_DGND

R sour TIMESTEP = 1.E IO_LEVEL=0

+ 0.000000s 0

+ 2.000000E-9s 1

.model delay ueff

.options digmntymx=2

.model source uio(drvh=50

drvl=50)

.probe

.tran 10ns 400ns

.end

Результат тестирования

Т-триггера приведен в приложении Г.

.model dinamics ueff

.model dinam ugate

.tran 10ns 400ns

.probe

.end

Результат тестирования работы формирователя пачек

импульсов приведен в приложениии Д.

3.2.8 Объединение моделей функциональных узлов и

тестирование

работы всей модели

синхронизирующего устройства

Тестирование всей модели

синхронизирующего устройства можно осуществить двумя способами.

Первый способ заключается

в непосредственном соединении всех разработанных моделей, входящих в устройство и представить

модель устройства ввиде одной программы.

Второй способ заключается

в создании библиотечных файлов таких логических элементов, как регистр, демультиплексер и счетчик. При составлении модели, в теле основной программы необходимо вставить операторы вызывающие

нужные библиотечные файлы.

Первый способ необходим

при создании и тестировании моделей несложных устройств, в которых модели различных логических элементов используются

не чаще одного раза.

Второй способ позволяет

избежать громоздких описаний моделей сложных устройств, в которые входит большое количество одинаковых элементов.

В данной работе удобнее

использовать первый способ.

Программная модель

синхронизирующего устройства приведена ниже.

Приложение Б

Виды используемых в работе вентилей и

тестирование работы

демультиплексера

INV

AND NAND

OR NOR

Рисунок Б.1 – Стандартные вентили используемые

в данной работе

Рисунок Б.2 – Результат тестирования модели демультиплексера

Приложение В

Результат

тестирования регистра и пример триггеров с динамическим

управлением

JKFF

DFF

|

Главная

Главная

Схемы

Схемы

Студентам

Студентам

Программы

Программы

Поиск

Поиск

Top50

Top50

Главная

Главная

Схемы

Схемы

Студентам

Студентам

Программы

Программы

Поиск

Поиск

Top50

Top50