Студентам > Рефераты > Развитие архитектуры материнских плат для PC

Развитие архитектуры материнских плат для PCСтраница: 2/3

Шины

Шина

- это канал пересылки данных, используемый совместно различными блоками

системы. Информация передается по шине в виде групп битов. В состав шины для

каждого бита слова может быть предусмотрена отдельная линия (параллельная

шина), или все биты слова могут последовательно во времени использовать одну

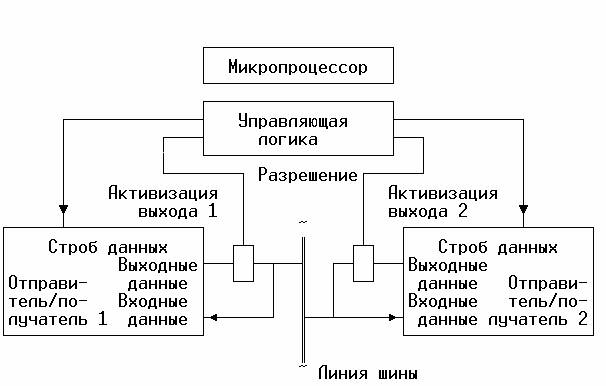

линию (последовательная шина). На рисунке показано типичное подключение

устройств к шине данных.

Шина

с тремя состояниями

Три

состояние на шине - это состояния высокого уровня, низкого уровня и 3-ее

состояние. 3-ее состояние позволяет устройству или процессору отключиться от

шины и не влиять на уровни, устанавливаемые на шине другими устройствами или

процессорами. Таким образом, только одно устройство является ведущим на шине.

Управляющая логика активизирует в каждый конкретный момент только одно

устройство, которое становиться ведущим. Когда устройство активизировано, оно

помещает свои данные на шину, все же остальные потенциальные ведущие

переводятся в пассивное состояние.

К

шине может быть подключено много приемных устройств. Сочетание управляющих и

адресных сигналов, определяет для кого именно предназначаются данные на шине.

Управляющая логика возбуждает специальные стробирующие сигналы, чтобы указать

получателю когда ему следует принимать данные. Получатели и отправители могут

быть однонаправленными и двунаправленными. На рисунке показаны двунаправленные

отправители/получатели, подключенные к шине.

Шинная

организация получила широкое распространение, поскольку в этом случае все

устройства используют единый протокол сопряжения модулей центральных

процессоров и устройств ввода/вывода с помощью трех шин.

Сопряжение

с центральным процессором осуществляется посредством трех шин: шины данных,

шины адресов и шины управления.

Шина

данных служит для пересылки данных между ЦП и памятью или ЦП и устройствами

ввода/вывода. Эти данные могут представлять собой как команды ЦП, так и

информацию, которую ЦП посылает в порты ввода/вывода или принимает оттуда. В МП

8088 шина данных имеет ширину 8 разрядов. В МП 8086, 80186, 80286 ширина шины

данных 16 разрядов; в МП 80386,80486,Pentium и Pentium Pro - 32 разряда.

Шина

адресов используется ЦП для выбора требуемой ячейки памяти или устройства

ввода/вывода путем установки на шине конкретного адреса, соответствующего одной

из ячеек памяти или одного из элементов ввода/вывода, входящих в систему. По

шине управления передаются управляющие сигналы, предназначенные памяти и

устройствам ввода/вывода.

Магистральная

организация предполагает наличие управляющего модуля. Основное назначение этого

модуля - организация передачи слова между двумя другими модулями.

Операция

на системной магистрали начинается с того, что управляющий модуль устанавливает

на шине кодовое слово модуля - отправителя и активизирует линию строба

отправителя. Это позволяет модулю, кодовое слово которого установлено на шине,

понять, что он является отправителем. Затем управляющий модуль устанавливает на

кодовое слово модуля - получателя и активизирует линию строба получателя. Это

позволяет модулю, кодовое слово которого установлено на шине, понять, что он

является получателем.

После

этого управляющий модуль возбуждает линию строба данных, в результате чего

содержимое регистра отправителя пересылается в регистр получателя. Этот шаг

может быть повторен любое число раз, если требуется передать много слов.

Данные

пересылаются от отправителя получателю в ответ на импульс, возбуждаемый

управляющим модулем на соответствующей линии строба. При этом предполагается,

что к моменту появления импульса строба в модуле - отправителе данные

подготовлены к передаче, а модуль - получатель готов принять данные. Такая

передача данных носит название синхронной (синхронизированной).

Процессы

на магистралях могут носить асинхронный характер. Передачу данных от

отправителя получателю можно координировать с помощью линий состояния, сигналы

на которых отражают условия работы обоих модулей. Как только модуль назначается

отправителем, он принимает контроль над линией готовности отправителя,

сигнализируя с ее помощью о своей готовности принимать данные. Модуль,

назначенный получателем, контролирует линию готовности получателя, сигнализируя

с ее помощью о готовности принимать данные.

При

передаче данных должны соблюдаться два условия. Во-первых, передача

осуществляется лишь в том случае, если получатель и отправитель сигнализируют о

своей готовности. Во-вторых, каждое слово должно передаваться один раз. Для

обеспечения этих условий предусматривается определенная последовательность

действий при передачи данных. Эта последовательность носит название протокола.

В

соответствии с протоколом отправитель, подготовив новое слово, информирует об

этом получателя. Получатель, приняв очередное слово, информирует об этом

отправителя. Состояние линий готовности в любой момент времени определяет

действия, которые должны выполнять оба модуля.

Каждый

шаг в передаче данных от одной части системы к другой называется циклом

магистрали (или часто машинным циклом). Частота этих циклов определяется

тактовыми сигналами ЦП. Длительность цикла магистрали связана с частотой

тактовых сигналов.

Первой

системной, разработанной для компьютеров PC/XT, в основе которых лежали

микропроцессоры, была шина PC/XT-bus. Она была 8-и разрядной, а ее контролер

обеспечивал работу на чистоте микропроцессора (4,77мгц). С появлением машин

типа PC/AT, использующих 16-и разрядные микропроцессоры 80286, а позже и 80386

(версия SX), была создана шина PC/AT-bus. В связи с ростом тактовой частоты

микропроцессоров до 12-16 МГц контролер выполнял ее деление пополам для

обеспечения приемлемой тактовой частоты работы шины.

ISA

На

базе этих двух шин был разработан международный стандарт ISA (Industry Standard Architecture), широко

использующийся в современных компьютерах. Типовая тактовая частота — 8 Мгц.

Деление частоты остается функцией контролеров системных шин, но поскольку

произошло дальнейшее увеличение тактовой частоты микропроцессоры до 25,33 и 50

Мгц, коэффициент деления был увеличен. Кроме увеличения разрядности увеличилось

количество прерываний (IRQ) и каналов прямого доступа в память (DMA) (в ISA 15

и 7 соответственно), а также функциональных и диагностических возможностей. В

тоже время сохранялась преемственность системных шин, в том числе на уровне

контактов разьемов. Благодаря этому в новых системах можно использовать

разработанные ранее контролеры и карты. Теоретическая пропускная способность

шины — 16 Мбайт/с, практически она ниже поскольку обмен данными по шине

производится за три такта работы процессора. Для слотов расширения на

материнской плате компьютеров с шиной ISA-16 устанавливается стандартная пара

разьемов (или один сдвоенный разъем) с числом контактов 62+36, а на шине ISA-8

устанавливается разъемы с 64-контактами.

EISA

С

появлением 32-разрядных микропроцессоров 80386 (версия DX) фирмами Compaq, NEC

и рядом других была создана 32-разрядная шина EISA (Extended ISA), полностью совместимая c ISA. Преемственность EISA с

ISA обеспечивается использованием “двухэтажного” разъема. Первый “этаж”-

стандартная шина ISA, что позволяет использовать ISA контролеры и карты,

разработанные как для ISA-16, так даже и для ISA-8. Шина EISA позволяет

автоматически производить конфигурацию и арбитраж запросов на обслуживание (bus mastering), что выгодно ее отличает от шины ISA.

VESA

Локальной

шиной (local bus) обычно называется шина, электрически выходящая

непосредственно на контакты микропроцессора, т.е. это шина процессора. Она

обычно объединяет процессор, память, схемы буферизации для системной шины и ее

контролер, а также некоторые другие вспомогательные схемы. Работы по созданию

локальной шины велись разными фирмами параллельно, но в конце концов была

создана ассоциация стандартов видео оборудования — Video Equipment Standard Association (VESA). Первая спецификация на стандарт локальной шины

появилась в 1992 году. Много было позаимствовано из архитектуры локальной шины

80486. Были разработанны только новый протокол обработки сигналов и топология

разьемов. Достоинствами VLB является высокая скорость обмена информации (шина

может работать в системе с процессором 80486DX-50). Но возникает зависимость от

частоты работы процессора (конструирование плат с широким частотным

диапазоном). Электрическая нагрузка не позволяет подключать более трех плат.

Кроме того, VLB не рассчитана на использование с процессорами, пришедшим на

замену 486-му или параллельно существующими с ними: Alpha, PowerPC и др.

Поэтому с середине 1993 года из ассоциации VESA вышел ряд производителей во

главе с Intel. Эти фирмы создали специальную группу для разработки нового

альтернативного стандарта, названную Peripheral Component Interconnect (PCI).

PCI

Разработка

шины и производство соответствующих компонентов заняли больше времени, чем для

VLB, и первые системы с шиной PCI появились только год спустя. Строго говоря

шина PCI не является локальной, а относится к классу mezzanine bus, поскольку

имеет между собой и локальной шиной процессора специальный узел — согласующий

мост. При этом стандарт PCI предусматривает использование контроллера, который

заботится о разделении управляющих сигналов шины и процессора и осуществляет

арбитраж по шине PCI, а также акселератор. Это делает шину процессорно

независимой.

Стандарт

PCI предусматривает несколько способов повышения пропускной способности. Один

из них — блочная передача последовательных данных (например графика, дисковые

файлы), что не требует времени на установку адреса каждого элемента. Более

того, акселератор может накапливать информацию в буферах, что обеспечивает

одновременный с чтением данных из памяти блочный обмен с периферийным

устройством. Другой способ ускорения передачи — мультиплексирование —

предусматривает передачу последовательных данных по адресным линиям, что

удваевает пропускную способность шины. Шина PCI использует установку прерываний

по уровню, что делает ее более надежной и привлекательной (в отличие от VLB).

Еще одно отличие — PCI работает на 33 Мгц, независимо то частоты процессора.

Теоретически пропускная способность шины 132 Мбайт/с. Реальная же пропускная способность

несколько больше половины от теоретической. Стандарт PCI предусматривает и

64-разрядную версию. Для 32-разрядной шины PCI используется 124-контактный

разъем, причем в нем предусмотрены ключи и контакты, предназначенные для оценки

необходимого для работы платы расширения напряжения питания (5В или 3,3В).

Тактовый

генератор

Большинство

логических элементов компьютера разработанно таким образом, что они должны

работать синхронно, то есть по определенным тактовым сигналам.

Контролер

прерываний

В

первых компьютерах использовалась микросхема контроллера прерываний i8259,

которая имеет 8 входов для сигналов прерываний. В IBM PC/AT восьми линий

прерываний стало уже недостаточно и их количество было увеличено до 15, путем

каскадного включения двух микросхем контролеров прерываний.

Память

Всем

компьютерам требуется память нескольких видов. Вся память делится на внутреннюю

и внешнюю. В компьютерных системах работа с памятью основывается на очень

простых концепциях — это сохранять один бит информации так, чтобы потом он мог

быть извлечен оттуда.

В

настоящее время широкое распространение получили устройства динамической памяти

базирующиеся на способности сохранять электрический заряд (конденсаторы). С

первого взгляда конденсатор не удовлетворяет основному требованию устройств

памяти. Он не способен сохранять заряд в течении длительного промежутка

времени, но он позволяет делать это в течении нескольких миллисекунд, что

вполне достаточно, чтобы использовать это в электронике. За это время

специальные цепи компьютера обеспечивают подзарядку конденсатора, то есть

обновление информации. Из-за непрерывности этого процесса такая память

называется динамической.

В

современных персональных компьютерах динамическая память реализуется на базе

специальных цепей проводников, заменивших обычные конденсаторы. Большое

количество таких цепей объединяются в корпусе одного динамического чипа. Однако

подобно памяти на конденсаторах, она должна постоянно освежаться.

В

то время как динамическая память, получив заряд электричества удерживает его,

так называемая статическая память, позволяет потоку электронов циркулировать по

цепи. Прикладываемое напряжение может изменить направление движения электронов.

Причем существует только два направления движения потока, что позволяет

использовать данные цепи в качестве элементов памяти. Статическая память

работает наподобие выключателя, который переключает направление электронного

потока.

Кроме

оперативной памяти существует еще и постоянная память(ПЗУ). Ее главное отличие

от ОЗУ - невозможность в процессе работы изменить состояние ячеек ПЗУ. В свою

очередь и эта память делится на постоянную и репрограммируемую. Принципы ее

функционирования понятны из названия.

Эволюция

микросхем ОЗУ вплотную связана с эволюцией персональных компьютеров. Для успеха

настольных компьютеров требовались миниатюрные чипы ОЗУ. По мере увеличения

емкости памяти цена скачкообразно возрастала, но потом постоянно уменьшалась по

мере отработки технологии и роста объемов производства.

Первые

PC реализовывались на стандартных RAM-чипах по 16 Кбит. Каждому биту

соответствовал свой собственный адрес.

Где-то

около года после представления XT появилось ОЗУ с большими возможностями и

более эффективное с точки зрения его цены. Хотя новые микросхемы могли вмещать

по 64 Кбит, она были дешевле чем 4 по 16 Кбит. Системная плата PC была создана

с учетом использования новых микросхем памяти. Через несколько лет 64 Кбитные

чипы стали настолько широко распространены, что стали дешевле чем 16 Кбитные

микросхемы.

К

1984 году был сделан еще один шаг по увеличению объема памяти в одном корпусе -

появились 256 - Кбитные микросхемы. И RAM чипы этого номинала были установлены

на первых AT. А сегодня микросхемы в 8 и 16 Мбайт стали обычным явлением.

PC

имел довольно простую архитектуру памяти, по крайней мере, если на нее смотреть

сейчас с высоты последних достижений компьютерной индустрии. Память PC была

представлена одним блоком, в котором каждый байт был доступен по указанию его

адреса.

Микросхемы

памяти были разбиты на 9 банков, использующих в ранних PC 16-Кбитные, а затем и

64-Кбитные микросхемы. Восемь микросхем выделяли по одному биту для организации

каждого байта памяти, девятая микросхема использовалась в качестве контрольного

бита четности.

Когда

микропроцессор 80286 стали использовать в AT и их аналогах, возникла проблема с

организацией архитектуры памяти. Обычные микросхемы памяти не могли работать в

таком быстром темпе, в котором работал микропроцессор. Поэтому пришлось

использовать статус ожидания, в случае когда процессор требовал информацию из

памяти, то есть микропроцессору приходилось зависать на один-два такта, что

давало возможность памяти обработать запрос.

Динамические

микросхемы памяти маркеруются специальным числом, говорящим об их скоростных возможностях.

Указанное на корпусе число отражает время доступа в наносекундах без последнего

нуля.

Время

доступа не является, однако, единственной или наиболее важной характеристикой

микросхем памяти. Более значимо такое понятие, как время цикла, которое говорит

о том, как быстро можно произвести повторное обращение. В динамических

микросхемах это время больше времени доступа, в статических чипах эти времена

равны, что говорит о более скоростных режимах последних.

Чтобы

справиться с ограничением по скорости, были использованы специальные решения по

организации памяти. Наиболее простое из них - это использование обычной

архитектуры с необходимым числом циклов ожидания.

Хорошая

альтернатива предыдущему методу - использование кэш-памяти, что позволит

избежать полного заполнения всей машины быстрой RAM памятью. Обычно программа

использует память какой либо ограниченной области. Храня нужную информацию в

кэш-памяти, работа с которой позволяет процессору обходиться без всяких циклов

ожидания.

Не

всякая кэш-память равнозначна. Большое значение имеет тот факт, как много

информации может содержать кэш-память. Чем больше кэш-память, тем больше

информации может быть в ней размещено, а следовательно, тем больше вероятность,

что нужный байт будет содержаться в этой быстрой памяти. Очевидно, сто самый

лучший вариант - это когда объём кэш-памяти соответствует объему всей

оперативной памяти. В этом случае вся остальная память становится не нужной.

Крайне противоположная ситуация - 1 байт кэш-памяти - тоже не имеет практического

значения, так как вероятность того, что нужная информация окажется в этом

байте, стремится к нулю. Практически, диапазон используемой кэш-памяти

колеблется в пределах 16-64К.

|

Главная

Главная

Схемы

Схемы

Студентам

Студентам

Программы

Программы

Поиск

Поиск

Top50

Top50

Главная

Главная

Схемы

Схемы

Студентам

Студентам

Программы

Программы

Поиск

Поиск

Top50

Top50