Студентам > Дипломные работы > Коммутатор цифровых каналов системы передачи

Коммутатор цифровых каналов системы передачиСтраница: 5/12

Тактируемые D-триггеры

используются в схеме приемника циклового и сверхциклового синхронизма

(на них собран регистр сдвига); у тактируемого триггера добавлен еще

один вход для синхроимпульса, по которому и срабатывает триггер.

Схема D-триггера, обозначение и таблица переходов приведены

на рисунке 7.1.

Рис. 7.1. Схема D-триггера.

Рассмотрим принцип работы триггера, его схема

содержит два входа: один информационный (D), а другой синхронизирующий (C).

При подаче логического нуля на вход С, как видно из

осциллограмм, состояние триггера не изменяется, т.к. сигнал не

проходит через элементы И-НЕ на входе схемы, и следовательно

состояние триггера не изменяется. При подаче на вход С

напряжения логической единицы, поступающий на вход D сигнал изменит состояние триггера, т.к. на один из входных

элементов И-НЕ поступит единица. При поступлении логической единицы на

вход D (на входе С действует напряжение

логической единицы), триггер перейдет в состояние, когда на выходе

Q действует напряжение логической единицы; а при поступлении

логического нуля триггер перейдет в состояние, когда на выходе

Q действует напряжение логического нуля.

7.1.2 СЧЕТЧИКИ.

Счетчики

присутствуют во всех частях схемы. Простейшим двоичным счетчиком будет

обыкновенный делитель на два, который при поступлении на вход

импульса, на выходе будет выдавать логическую единицу до тех пор,

пока на вход не поступят еще один импульс. Такой делитель можно

собрать на одном D-триггере, соединив выход

Q со входом D и снимая информацию с этого же выхода.

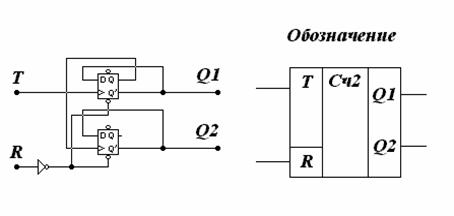

Двухразрядный счетчик импульсов получится объединении двух делителей на

два, причем вход С второго делителя необходимо присоединить к

выходу Q первого делителя. Схема двухразрядного двоичного

счетчика приведена на рисунке 7.2. Счетчики

присутствуют во всех частях схемы. Простейшим двоичным счетчиком будет

обыкновенный делитель на два, который при поступлении на вход

импульса, на выходе будет выдавать логическую единицу до тех пор,

пока на вход не поступят еще один импульс. Такой делитель можно

собрать на одном D-триггере, соединив выход

Q со входом D и снимая информацию с этого же выхода.

Двухразрядный счетчик импульсов получится объединении двух делителей на

два, причем вход С второго делителя необходимо присоединить к

выходу Q первого делителя. Схема двухразрядного двоичного

счетчика приведена на рисунке 7.2.

Рис. 7.2. Схема простейшего двухразрядного

счетчика.

Принцип работы данной схемы заключается в

следующем, при подаче первого импульса на вход схемы (Т)

входной триггер переходит в состояние, когда на выходе Q

действует логический ноль, при этом на инверсном выходе образуется

логическая единица, поступающая на вход D. Следовательно, при

поступлении следующего импульса логическая единица на входе

D «перебросит» триггер в состояние, когда на выходе

Q начинает действовать логическая единица, запускающая второй

триггер, который работает аналогичным образом. Таким образом, на

выходах схемы формируется последовательность двоичных чисел (см.

осциллограммы на рис. 7.2), сначала 00, затем 01, затем 10

и, наконец, 11; после поступления следующего импульса на вход Т,

на выходе снова образуется 00.

|

|

|

|

|

У приведенного выше счетчика существует

один недостаток, его нельзя «сбросить» в исходное, нулевое состояние.

Этот недостаток легко устраним, т.к. у D-триггера

имеется возможность вывести еще один вход для сброса триггера в

нулевое состояние ®, тогда схема такого счетчика примет следующий вид

(см. рис. 7.3).

Рис. 7.3 Двухразрядный счетчик.

Принцип работы данной схемы не отличается от

принципа работы схемы приведенной выше, за исключением того, что в

нулевое состояние (на выходе 00) эту схему можно перевести в

любой момент времени по сигналу R.

При необходимости увеличить разрядность

счетчика можно, добавляя в схему новые триггеры (таким образом

строятся схемы на 3, 4 и более разрядов), но иногда возникает

необходимость сбросить не все выходы счетчика, а лишь один разряд.

Такую схему можно построить, добавив элемент ИЛИ-НЕ, подключенный к

триггеру обслуживающему заданный разряд. Рассмотрим схему

четырехразрядного счетчика, с возможностью сброса четвертого разряда.

Схема такого устройства представлена на рисунке 7.4.

Рис. 7.4. Схема четырехразрядного счетчика с

возможностью сброса четвертого разряда.

Принцип работы данной схемы практически не

отличается от принципа работы счетчика, рассмотренного выше, кроме

того, что сброс четвертого разряда может осуществляться как вместе со

сбросом всего счетчика, так и отдельно, для этого в схему добавлен

элемент ИЛИ-НЕ.

7.1.3 ДЕШИФРАТОРЫ

Дешифраторы, как и счетчики, встречаются во всех элементах схемы.

Применяемые в устройстве дешифраторы являются позиционными, они

преобразуют двоичный код в импульс на соответствующем коду номере

выхода. Для построения такой схемы, в отличие от предыдущих, не

нужно использовать элементы с памятью (такие как триггеры), ее можно

собрать лишь из схем НЕ и И. Схема трехразрядного дешифратора

представлена на рисунке 7.5.

Рис. 7.5.

Схема трехразрядного дешифратора.

Схема работает следующим образом, при

поступлении кодовой комбинации (от 000 до 111) на вход

ищется совпадение (при помощи схем И) и на соответствующий выход

поступает напряжение логической единицы. Инверторы требуются для

преобразования кодовых комбинаций, содержащих логические нули.

В разрабатываемой БИС существует необходимость

и в дешифраторах на большее количество разрядов (4 и 5), поэтому

необходимо рассмотреть схемы таких дешифраторов. Принципы

функционирования таких схем не отличаются от принципа функционирования

трехразрядного дешифратора, только количество схем совпадения (И)

увеличивается в соответствии с увеличением выходов (N):

N = 2n;

[7.1]

где n

- количество входов, и количество инверторов увеличится до количества

входов.

Схема дешифратора на четыре входа представлена

на рисунке 7.6. Аналогично строится схема и пятиразрядного

дешифратора.

Рис. 7.5. Схема четырехразрядного дешифратора.

7.1.4 МУЛЬТИПЛЕКСОР

Мультиплексор является устройством, подключающим

один из входов к выходу по сигналу управления. В схеме

проектируемого устройства мультиплексор встречается всего один раз, но

так как схема его получается достаточно простой, то было решено

вынести мультиплексор в библиотеку элементов. У разрабатываемого

мультиплексора 10 информационных входов, разбитых на две группы по 5

входов, и 5 выходов, к которым подключается соответствующая группа

входов, управление производится при помощи одного управляющего входа.

Схема такого мультиплексора представлена на рисунке 7.6.

Рассмотрим принцип работы данной схемы, при

поступлении на вход А уровня логического нуля через инвертор

подключаются схемы совпадения для первой группы входов, при

прохождении через любой из входов этой группы сигнала логической

единицы, одна из схем И срабатывает и выдает на своем выходе

напряжение логической единицы, через схему ИЛИ подключены выходы, и

при поступлении на один из входов схемы ИЛИ, сигнал проходит на

выход. При подаче напряжения логической единицы на вход А первая

группа входов отключается, и подключается вторая группа входов, схема

работает в аналогичном первому случаю режиме, только на выход

поступают сигналы со второй группы входов. Этот принцип работы хорошо иллюстрируется

при помощи осциллограмм приведенных на рисунке 7.6.

Рис. 7.6.

Схема мультиплексора.

7.2 РАЗРАБОТКА ПРИНЦИПИАЛЬНЫХ СХЕМ БЛОКОВ ПРОЕКТИРУЕМОЙ БИС

7.2.1 РАЗРАБОТКА

ПРИНЦИПИАЛЬНОЙ СХЕМЫ ПРИЕМНИКА ЦИКЛОВОГО И СВЕРХЦИКЛОВОГО СИНХРОНИЗМА

Разработку принципиальной схемы на основе

разработанной библиотеки элементов необходимо вести по функциональной

схеме данного блока. В функциональной схеме имеется регистр сдвига на

тактируемых триггерах (следовательно, нам понадобятся 8 D-триггеров),

схемы совпадения собраны на собраны на элементах И (на 4 и на 6

входов), счетчики и дешифраторы также являются библиотечными

элементами, следовательно, по сравнению с функциональной схемой

принципиальная не несет в себе изменений. Принципиальная схема,

построенная с помощью программы схемотехнического моделирования,

представлена на рисунке 7.7, единственным отличием, связанным со

спецификой программы является построение схемы в стандарте ANSI. Функционирование схемы, подробно описано в ГЛАВЕ

3.

|

Главная

Главная

Схемы

Схемы

Студентам

Студентам

Программы

Программы

Поиск

Поиск

Top50

Top50

Главная

Главная

Схемы

Схемы

Студентам

Студентам

Программы

Программы

Поиск

Поиск

Top50

Top50