# **TDA1180P**

# TV HORIZONTAL PROCESSOR

- NOISE GATED HORIZONTAL SYNC SEPARA-TOR

- NOISE GATED VERTICAL SYNC SEPARATOR

- HORIZONTAL OSCILLATOR WITH FRE-QUENCY RANGE LIMITER

- PHASE COMPARATOR BETWEEN SYNC PULSES AND OSCILLATOR PULSES (PLL)

- PHASE COMPARATOR BETWEEN FLYBACK PULSES AND OSCILLATOR PULSES (PLL)

- LOOP GAIN AND TIME CONSTANT SWITCH-ING ( VCR)

- COMPOSITE BLANKING AND KEY PULSE GENERATOR

- PROTECTION CIRCUITS

- OUTPUT STAGES WITH HIGH CURRENT CA-PABILITY

#### **DESCRIPTION**

The TDA1180P is a horizontal processor circuit for b.w. and colour monitors. It is a monolithic integrated circuit encapsulated in 16-lead dual in-line plastic package.

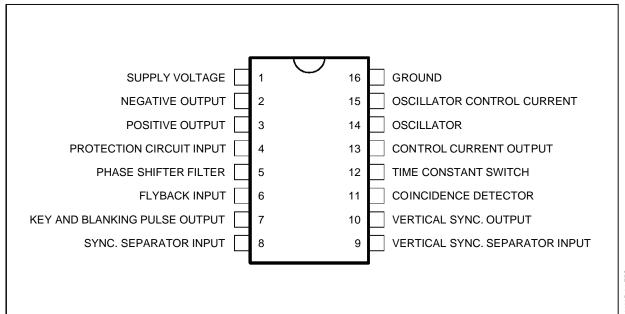

#### **PIN CONNECTIONS**

May 1993 1/12

180P-01.EPS

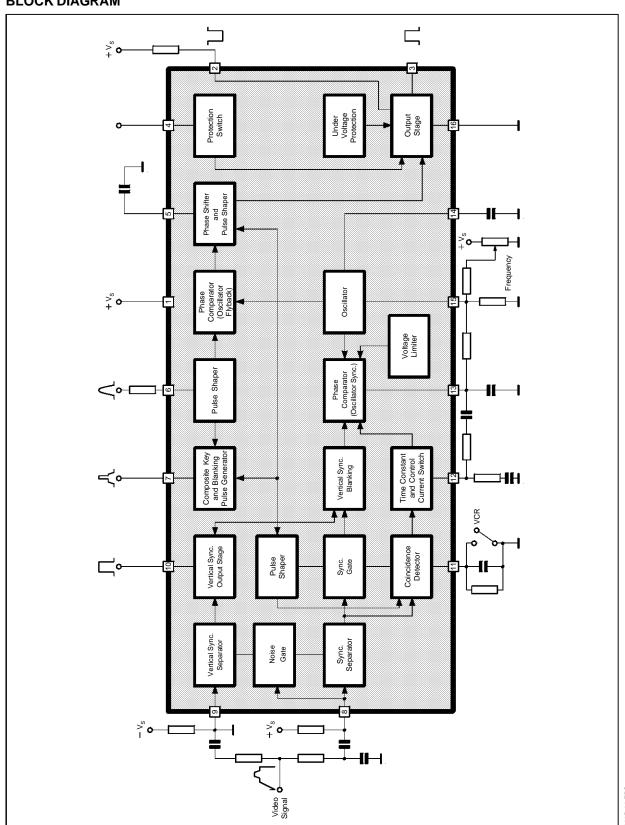

# **BLOCK DIAGRAM**

1180P-02.EPS

# **ABSOLUTE MAXIMUM RATINGS**

| Symbol                            | Parameter                              | Value                | Unit |

|-----------------------------------|----------------------------------------|----------------------|------|

| Vs                                | Supply voltage (Pin 1)                 | 15                   | V    |

| V <sub>2</sub>                    | Voltage at Pin 2                       | 18                   | V    |

| V <sub>4</sub>                    | Voltage at Pin 4                       | Vs                   |      |

| V <sub>8</sub>                    | Voltage at Pin 8                       | - 6 , V <sub>S</sub> | V    |

| V <sub>9</sub>                    | Voltage at Pin 9                       | ± 6                  | V    |

| V <sub>11</sub>                   | Voltage at Pin 11                      | Vs                   |      |

| l <sub>2</sub>                    | Pin 2 peak current                     | 1                    | Α    |

| l <sub>3</sub>                    | Pin 3 peak current                     | 0.5                  | А    |

| I <sub>6</sub>                    | Pin 6 current                          | 30                   | mA   |

| l <sub>7</sub>                    | Pin 7 current                          | 20                   | mA   |

| I <sub>10</sub>                   | Pin 10 current                         | 30                   | mA   |

| Ptot                              | Total power dissipation at Tamb ≤ 70°C | 1                    | W    |

| T <sub>stg</sub> , T <sub>j</sub> | Storage and junction temperature       | - 40 , + 150         | °C   |

180P-01.TBL

# THERMAL DATA

| Symbol                | Parameter                               | Value | Unit |

|-----------------------|-----------------------------------------|-------|------|

| R <sub>th (j-a)</sub> | Thermal Resistance Junction-Ambient Max | 80    | °C/W |

# **ELECTRICAL CHARACTERISTICS**

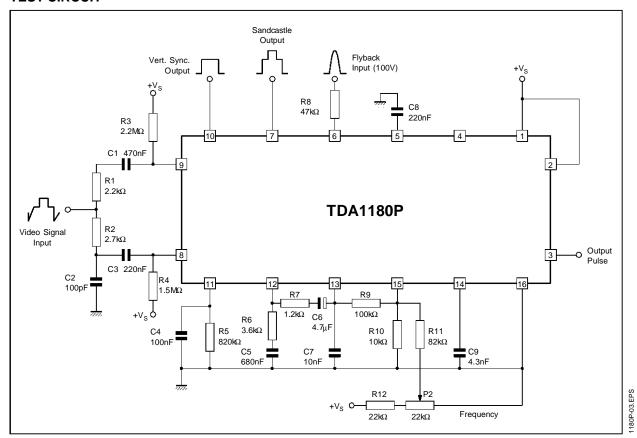

(refer to the test circuit,  $V_S = 12V$ ,  $T_A = 25$ °C, unless otherwise specified)

| Symbol | Parameter                                                                   | Test conditions    | Min. | Тур. | Max. | Unit |

|--------|-----------------------------------------------------------------------------|--------------------|------|------|------|------|

| Vs     | Supply voltage range                                                        |                    | 9.5  | 12   | 13.2 | V    |

| Is     | Supply current                                                              | I <sub>3</sub> = 0 |      | 42   | 52   | mA   |

| Vs     | Supply voltage at which the output pulses (at pin 2 and 3) are switched off |                    |      |      | 4    | V    |

# HORIZONTAL SYNC. SEPARATOR

| Vı             | Peak to peak input signal |                        | 1 | 3   | 6 | V  |

|----------------|---------------------------|------------------------|---|-----|---|----|

| V <sub>8</sub> | Input switching voltage   | Ι <sub>8</sub> = 80 μΑ |   | 1.5 |   | ٧  |

| I <sub>8</sub> | Input switching current   | V <sub>8</sub> = 1.4V  |   | 10  |   | μΑ |

| l <sub>8</sub> | Leakage current           | V <sub>8</sub> = -5V   |   |     | 1 | μΑ |

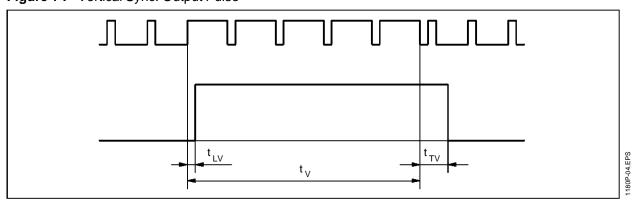

## VERTICAL SYNC. SEPARATOR

| $V_{I}$         | Peak to Peak Input Signal                               |                       | 1  | 3   | 6 | V  |

|-----------------|---------------------------------------------------------|-----------------------|----|-----|---|----|

| V <sub>9</sub>  | Input Switching Voltage                                 | I <sub>9</sub> = 80μA |    | 1.5 |   | V  |

| l <sub>9</sub>  | Input Switching Current                                 | V <sub>9</sub> = 1.4V |    | 5   |   | μΑ |

| l <sub>9</sub>  | Leakage Current                                         | V <sub>9</sub> = -5V  |    |     | 1 | μΑ |

| V <sub>10</sub> | Vertical Sync. Pulse Output Voltage                     | No Load Pin10         | 11 |     |   | V  |

| R <sub>10</sub> | Output Resistance                                       |                       |    | 10  |   | kΩ |

| $t_{LV}$        | Delay between Leading Edge of Input and Output Signals  |                       |    | 17  |   | μs |

| t <sub>LV</sub> | Delay between Trailing Edge of Input and Output Signals |                       |    | 50  |   | μs |

| t <sub>V</sub>  | Vertical Sync Pulse Duration                            |                       |    | 190 |   | μs |

30P-03.TBL

# **ELECTRICAL CHARACTERISTICS** (continued)

(refer to the test circuit,  $V_S = 12V$ ,  $T_A = 25^{\circ}C$ , unless otherwise specified)

| Symbol            | Parameter                                                                                  | Test conditions                                                  | Min.   | Тур.      | Max.  | Unit    |

|-------------------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------|--------|-----------|-------|---------|

| PROTECT           | ION CIRCUIT                                                                                |                                                                  |        |           |       |         |

| V <sub>4</sub>    | Input Voltage for Switching off the Output Pulses                                          | Output Pulses OFF<br>Output Pulses ON                            | 1      |           | 0.5   | V       |

| R <sub>4</sub>    | Input Resistance                                                                           |                                                                  |        | 200       |       | kΩ      |

| <b>l</b> 4        | Input Current                                                                              |                                                                  | 5      |           |       | μΑ      |

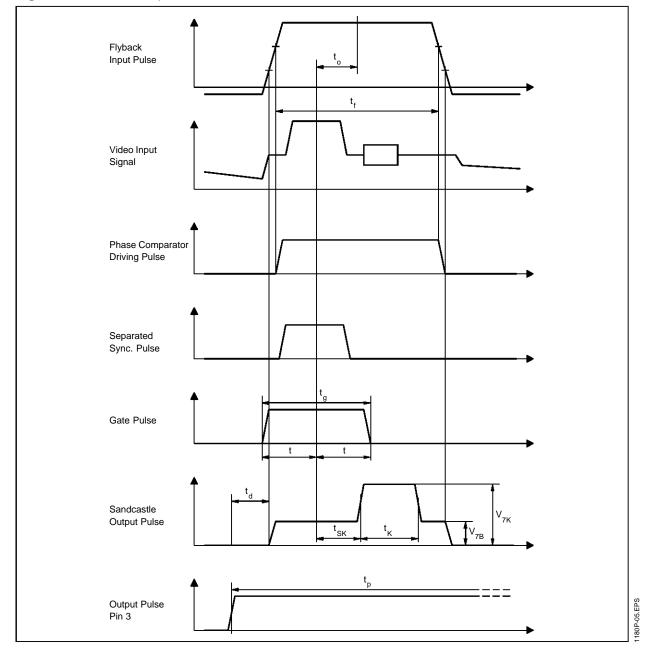

| FLYBACK           | PULSE                                                                                      |                                                                  |        |           |       |         |

| V <sub>6</sub>    | Input Threshold Voltage of Blanking Generator                                              |                                                                  |        | 1.8       |       | V       |

| V <sub>6</sub>    | Input Threshold Voltage of Phase Comparator                                                |                                                                  |        | 7.6       |       | V       |

| I <sub>6</sub>    | Input Switching Current                                                                    | V <sub>6</sub> ≥ 1.7V                                            |        | 0.45      |       | mA      |

| OUTPUT F          | PULSE                                                                                      |                                                                  |        |           |       |         |

| V <sub>3</sub>    | Peak-to-Peak Output Voltage                                                                | I <sub>3</sub> = 150 mApp                                        |        | 10        |       | V       |

| l <sub>3</sub>    | Output Current                                                                             | V <sub>3</sub> = 5V                                              |        | 500       |       | mA      |

| R <sub>3</sub>    | Output Resistance                                                                          | At Leading Edge of output pulse At Training Edge of Output Pulse |        | 3<br>20   |       | Ω       |

| t <sub>p</sub>    | Output Pulse Duration                                                                      |                                                                  | 20     | 22        | 26    | μs      |

| COMPOSI           | TE BLANKING AND KEY PULSE                                                                  |                                                                  |        |           |       |         |

| V <sub>7k</sub>   | Key Pulse Output Peak Voltage                                                              |                                                                  | 9      | 11        |       | V       |

| V <sub>7B</sub>   | Blanking Pulse Output Voltage                                                              |                                                                  | 4.2    | 4.5       | 4.8   | V       |

| R <sub>7</sub>    | Output Resistance                                                                          |                                                                  |        | 100       |       | Ω       |

| t <sub>sk</sub>   | Phase Relation Between Trailing Edge of Key Pulse and Middle of Sync. Input Pulse          |                                                                  |        | 2.7       |       | μs      |

| t <sub>k</sub>    | Key Pulse Duration                                                                         |                                                                  | 3.5    | 3.8       |       | μs      |

| t <sub>fb</sub>   | Delay between Flyback Pulse and Blanking Pulse                                             | V <sub>6</sub> = 1.7V                                            |        |           | 0.2   | μs      |

| INTERNAL          | GATING PULSE                                                                               |                                                                  |        |           |       |         |

| t <sub>g</sub>    | Gating Pulse Duration                                                                      |                                                                  |        | 7.5       |       | μs      |

| t                 | Phase Relation between Middle of Sync. Pulse and Trailing and Leading Edge of Gating Pulse |                                                                  |        | 3.75      |       | μs      |

| COINCIDE          | NCE DETECTOR                                                                               |                                                                  |        |           |       |         |

| V <sub>11</sub>   | Output Voltage                                                                             | With Coincidence<br>Without Coincidence                          |        | 6.8       | 4     | V       |

| I <sub>11</sub>   | Peak Output Current                                                                        |                                                                  |        | 0.5       |       | mA      |

| VCR SWIT          | СН                                                                                         |                                                                  | · ·    |           |       |         |

| V <sub>11</sub>   | Input Voltage                                                                              |                                                                  | 0 to 4 | 4 or 8.5  | to 12 | V       |

| - I <sub>11</sub> | Output Current                                                                             |                                                                  | 35     |           |       | μΑ      |

| I <sub>11</sub>   | Output Current                                                                             |                                                                  | 0.4    |           |       | mA      |

| TIME CON          | ISTANT SWITCH                                                                              |                                                                  |        |           |       |         |

| V <sub>12</sub>   | Output Voltage                                                                             |                                                                  |        | 3         |       | V       |

| R <sub>12</sub>   | Output Resistance                                                                          | $4.5V < V_{11} < 8V$<br>$V_{11} > 8.5V$ or $V_{11} < 4V$         |        | 100<br>40 |       | Ω<br>kΩ |

**ELECTRICAL CHARACTERISTICS** (continued) (refer to the test circuit,  $V_S = 12V$ ,  $T_A = 25^{\circ}C$ , unless otherwise specified)

| Symbol                               | Parameter                                                                             | Test conditions | Min.             | Тур.                            | Max. | Unit             |

|--------------------------------------|---------------------------------------------------------------------------------------|-----------------|------------------|---------------------------------|------|------------------|

| OSCILLAT                             | OR                                                                                    |                 |                  |                                 |      |                  |

| V <sub>14</sub>                      | Low Level Threshold Voltage                                                           |                 |                  | 5.4                             |      | V                |

| V <sub>14</sub>                      | High Level Threshold Voltage                                                          |                 |                  | 8.2                             |      | V                |

| l <sub>14</sub>                      | Charge Current                                                                        |                 |                  | 0.6                             |      | mA               |

| I <sub>14</sub>                      | Discharge Current                                                                     |                 |                  | 0.3                             |      | mA               |

| V <sub>15</sub>                      | Current Source Supply Voltage                                                         |                 |                  | 3                               |      | V                |

| I <sub>15</sub>                      | Current Source Supply Current                                                         |                 |                  | 0.3                             |      | mA               |

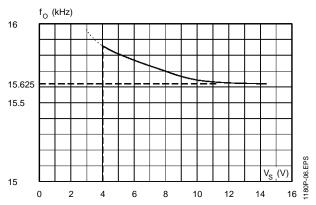

| f <sub>O</sub>                       | Free Running Frequency                                                                |                 |                  | 15625                           |      | Hz               |

| $\frac{\Delta f_{O}}{f_{O}}$         | Adjustment Range                                                                      |                 |                  | ± 10                            |      | %                |

| $\frac{\Delta f_{O}}{\Delta l_{15}}$ | Frequency Control Sensitivity                                                         |                 |                  | 52                              |      | <u>Hz</u><br>μA  |

| $\Delta f_{O}$                       | Frequency Change when V <sub>S</sub> Drops to 4V                                      |                 |                  |                                 | ± 10 | %                |

| OSCILLAT                             | OR-FLYBACK PULSE PHASE COMPARATOR                                                     |                 |                  | •                               | •    |                  |

| V <sub>5</sub>                       | Control Voltage Range                                                                 |                 |                  | 9.4 to 8.                       | 2    | V                |

| l <sub>5</sub>                       | Peak Control Current                                                                  |                 | -0.6             |                                 | +0.6 | mA               |

| l <sub>5</sub>                       | Input Current (blocked Phase Detector)                                                |                 |                  |                                 | 5    | μΑ               |

| t <sub>D</sub>                       | Permissible Delay between Output Pulse Leading<br>Edge and Flyback Pulse Leading Edge |                 |                  | t <sub>p</sub> - t <sub>f</sub> |      | μs               |

| $\frac{\Delta t}{\Delta t_D}$        | Static Control Error                                                                  |                 |                  |                                 | 0.2  | %                |

| SYNC PUL                             | LSE-OSCILLATOR PHASE COMPARATOR                                                       |                 |                  | 1                               | l    | <u> </u>         |

| V <sub>13</sub>                      | Control Voltage Range                                                                 |                 | 4.6<br>to<br>1.4 |                                 |      | V                |

| I <sub>13</sub>                      | Control Peak Current                                                                  |                 | +2               | -2.2                            | -2   | mA               |

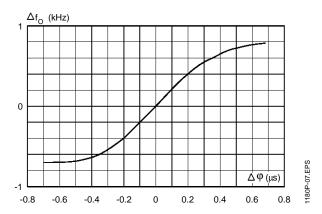

| $\frac{\Delta f}{\Delta t}$          | Phase Lock Loop Gain                                                                  |                 |                  | 2                               |      | <u>kHz</u><br>μs |

| f                                    | Catching and Holding Range                                                            |                 |                  | ± 700                           |      | Hz               |

| OVERALL                              | PHASE RELATIONSHIP                                                                    |                 | -                | 1                               |      |                  |

| to                                   | Phase Relation between Middle of Flyback Pulse and Middle of Sync. Pulse              |                 |                  | 2.2                             |      | μs               |

| $\frac{\Delta V_5}{\Delta t_O}$      | Adjustment Sensitivity                                                                |                 |                  | 65                              |      | mV<br>μs         |

| $\frac{\Delta l_5}{\Delta t_O}$      | Adjustment Sensitivity                                                                |                 |                  | 16                              |      | μA<br>μs         |

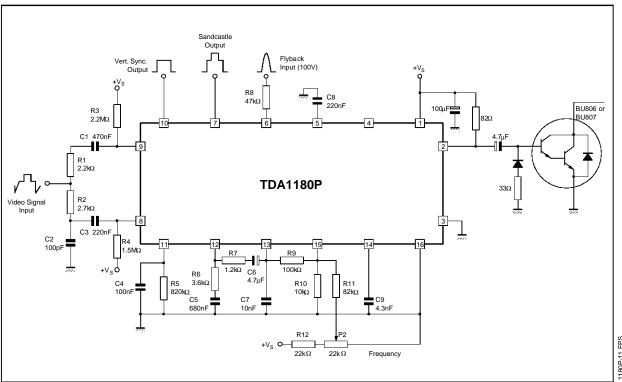

# **TEST CIRCUIT**

Figure 1: Vertical Sync. Output Pulse

Figure 2: Relation Ship of Main Waveform Phases

Figure 3: Free Running Frequency versus Supply Voltage

#### APPLICATION INFORMATION

### Pin 1 - Positive supply

The operating supply voltage of the device ranges from 10V to 13.2V

# Pin 2 and 3 - Output

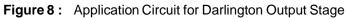

The outputs of TDA1180P are suitable for driving transistor output stages, they deliver positive pulse at Pin 3 and negative pulse at Pin 2.

The negative pulse is used for direct driving of the output stage, while positive pulse is useful when a driver stage is required.

The rise and fall times of the output pulses are about 150 ns so that interference due to radiation are avoided.

Furthermore the output stages are internally protected against short circuit.

#### Pin 4 - Protection circuit input

By connecting Pin 4 of the IC to earth the output pulses at Pin 2 and 3 are shut off; this function has been introduced to produced to protect the final stages from overloads.

The same pulses are also shut off when the supply voltage falls below 4V.

#### Pin 5 - Phase shifter filter

To compensate for the delay introduced by the line final stages, the flyback pulses to Pin 6 and the oscillator waveform are compared in the oscillator-flyback pulse phase comparator.

The result of the comparison is a control current which, after it has been filtered by the external capacitor connected to Pin 5, is sent to a phase shifter which adequately regulates the phase of the output pulses.

Figure 4: Loop Gain

The maximum phase shift allowed is:  $t_d = t_p - t_f$  where  $t_f$  is the flyback pulse duration.

Pin 5 has high input and output resistance (current generator).

#### Pin 6 - Flyback input

The flyback pulse drives the high impedance input through a resistor in order to limit the input current to suitable maximum values.

The flyback input pulses are processed by a double threshold circuit; this generates the blanking pulses by sensing low level flyback voltage and the pulses to drive the phase comparator by sensing high level flyback voltage, therefore phase jitter caused by ringing normally associated with the flyback pulse, is avoided.

#### Pin 7 - Key and blanking pulse output

The key pulse for taking out the burst from the chrominance signal is generated from the oscillator ramp and has therefore a fixed phase position with respect to the sync.

The key pulse is then added internally to the blanking pulse obtained by correctly forming the flyback pulse present at Pin 6.

The sum of the two signals (sandcastle pulse) is available on low impedance at output Pin 7.

## Pin 8 and 9 - Sync separators inputs

The video signal is applied by means of two distinct biasing networks to pins 8 and 9 of the IC and therefore to the respective vertical and horizontal sync separators.

The latter take the sync pulses out of the video signal and make them available to the rest of the circuit for further processing.

## Pin 10 - Vertical sync output

The vertical sync pulse, obtained by internal integration of the synchronizing signal, is available at this pin.

The output impedance is typically  $10k\Omega$  and the lowest amplitude without load is 11V.

#### Pin 11 - Coincidence detector

From the oscillator waveform a gate pulse 7  $\mu$ s wide is taken whose phase position is centered on the horizontal synchronism.

The gate pulse not only controls a logic block which permits the sync to reach the oscillator-sync phase comparator only for as long as its duration, but also allows the latching and de-latching conditions of the oscillator to be established. This function is obtained by a coincidence detector which compares the phase of the gate pulses with that of the sync.

When the two signals are not accurately aligned in time it means that the oscillator is not synchronized. In this case the detector acts on the logic block to eliminate its filtering effect and on the time constant switching block to establish a high impedance on Pin 12 (small time constant of low-pass filter).

This latter block also acts on the oscillator-sync phase detector to increase its sensitivity and with it the loop gain of the synchronizing system.

In this conditions the phase lock has low noise immunity (wide equivalent noise bandwidth) and rapid pull-in time which allows fairly short synchronization times.

Once locking has taken place the coincidence detector enables the logic block, causes a low impedance on Pin 12 and reduces the sensitivity of the phase comparator.

In these conditions the phase lock has high noise immunity (narrow equivalent noise bandwidth) due to the complete elimination of interference which occurs during the scanning period and the greater inertia with which the oscillator can change its frequency.

To optimize the behaviour of the IC if a video

recorder is used, the state of the detector can be forced by connecting Pin 11 to earth or to + V<sub>S</sub>. The characteristics of the phase lock thus correspond to the lack of synchronization.

Pin 12 - Time constant switch, (see Pin 11)

#### Pin 13 - Control current output

The oscillator is synchronized by comparing the phase of its waveform with that of the sync pulses in the oscillator-sync phase comparator and sending its output current I13 (proportional to the phase difference between the two signals) to Pin 15 of the oscillator after it has been filtered properly with an external low-pass circuit.

The time constant of the filter can be switched between two values according to the impedance presented by Pin 12.

The voltage limiter at the output of the phase comparator limits the voltage excursion on Pin 13 and therefore the frequency range in which the oscillator remains held-in.

The output resistance of Pin 13 is:

- low when V13 > 4.3 or V13 < 1.6V

- high when 1.6V < V13 < 4.3V

To prevent the vertical sync from reaching the oscillator-sync phase comparator along with the horizontal sync, a signal which inhibits the phase detector during the vertical interval is taken from the vertical output stage; inhibition remain even if the video signal is not present.

The free running frequenc of the oscillator is determined by the values of the capacitor and of the resistor connected to Pins 14 and 15 respectively. To generate the line frequency output pulses, two theresholds are fixed along the fall ramp of the triangular waveform of the oscillator.

Pin14 - Oscillator (see Pin 13)

Pin 15 - Oscillator control current input (see Pin 13)

Pin 16 - Ground

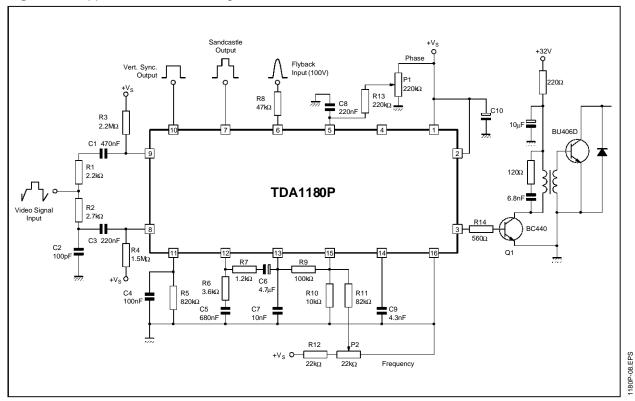

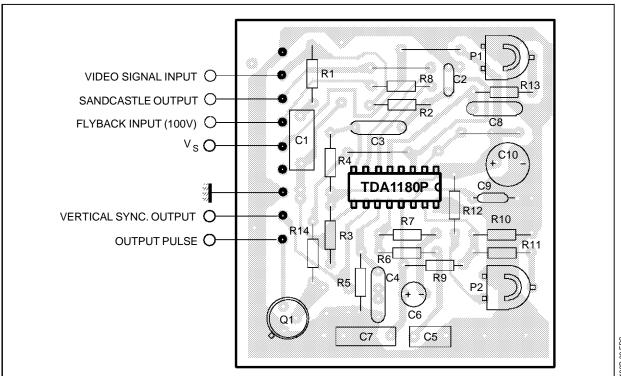

Figure 5: Application Circuit for Large Screen Black & White and Colour TV

Figure 6: P.C. Board and Component Layout for the Circuit in Figure 6 (1:1 scale)

1180P-09.EPS

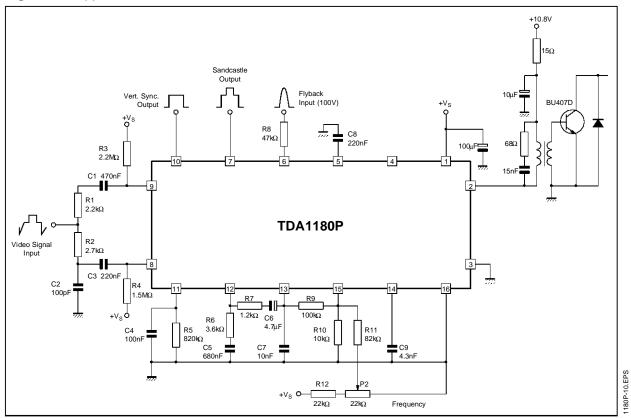

Figure 7: Application Circuit for Small Screen b.w. TV

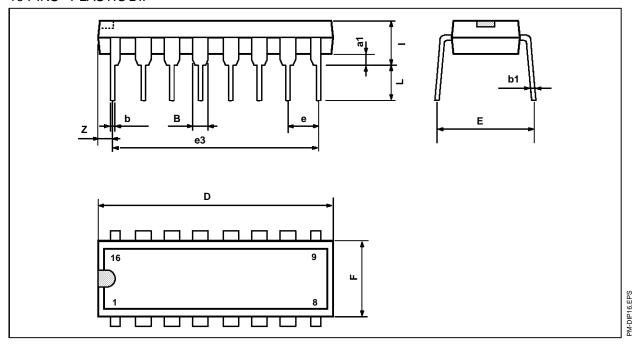

#### PACKAGE MECHANICAL DATA

16 PINS - PLASTIC DIP

| Dimensions |      | Millimeters |      |       | Inches |       |

|------------|------|-------------|------|-------|--------|-------|

|            | Min. | Тур.        | Max. | Min.  | Тур.   | Max.  |

| a1         | 0.51 |             |      | 0.020 |        |       |

| В          | 0.77 |             | 1.65 | 0.030 |        | 0.065 |

| b          |      | 0.5         |      |       | 0.020  |       |

| b1         |      | 0.25        |      |       | 0.010  |       |

| D          |      |             | 20   |       |        | 0.787 |

| E          |      | 8.5         |      |       | 0.335  |       |

| е          |      | 2.54        |      |       | 0.100  |       |

| e3         |      | 17.78       |      |       | 0.700  |       |

| F          |      |             | 7.1  |       |        | 0.280 |

| i          |      |             | 5.1  |       |        | 0.201 |

| L          |      | 3.3         |      |       | 0.130  |       |

| Z          |      |             | 1.27 |       |        | 0.050 |

P16.TBL

Information furnished is believed to be accurate and reliable. However, SGS-THOMSON Microelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No licence is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. SGS-THOMSON Microelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of SGS-THOMSON Microelectronics.

#### © 1994 SGS-THOMSON Microelectronics - All Rights Reserved

Purchase of I<sup>2</sup>C Components of SGS-THOMSON Microelectronics, conveys a license under the Philips I<sup>2</sup>C Patent. Rights to use these components in a I<sup>2</sup>C system, is granted provided that the system conforms to the I<sup>2</sup>C Standard Specifications as defined by Philips.

#### SGS-THOMSON Microelectronics GROUP OF COMPANIES

Australia - Brazil - China - France - Germany - Hong Kong - Italy - Japan - Korea - Malaysia - Malta - Morocco The Netherlands - Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A.